# ALMA Digital Front-End: Configuration Study. Final Report

Version 2.0

A. M. Baryshev<sup>1</sup> A. Khudchenko<sup>1</sup> S. Ashton<sup>2</sup> A. Baudry<sup>3</sup> R. Finger<sup>4</sup> N. Whyborn<sup>5</sup> J. Weintroub<sup>6</sup> A. Wootten<sup>2</sup> T. Mroczkowski<sup>7</sup> A. Gonzalez<sup>8</sup> T. Kojima<sup>8</sup> F. P. Mena<sup>4</sup> S. Gauffre<sup>3</sup> B. Klein<sup>9</sup>

December 16, 2020

<sup>1</sup> Kapteyn Astronomical Institute, RUG, Netherlands

<sup>2</sup> National Radio Astronomy Observatory, AUI, USA

$^3$  University of Bordeaux, Laboratoire d'astrophysique de Bordeaux, France

$^{\rm 4}$  Astronomy Department, University of Chile

<sup>5</sup> ALMA Observatory, Chile

CTA, Chile

Harvard-Smithsonian Center for Astrophysics, Cambridge, MA, USA

European Southern Observatory, Garching b. München, Germany

<sup>8</sup> National Astronomical Observatory of Japan, Mitaka, Japan

<sup>9</sup> Max Planck Institute for Radioastronomy, Bonn, Germany

#### Abstract

This report contains an analysis and trade-off study of an ALMA Digital Front-End (DFE) system which includes the digitizers and digital processing in the ALMA receiver cabin, and the digital transport system between the antennas and the centrally located correlator. A revised set of ALMA front-end requirements are proposed. The trade-off between different digitization and signal processing architectures is discussed in the context of a projection of relevant technology development over the next decade. DFE functions are described, including coarse frequency channelization, baseline ripple correction, digital image sideband leakage correction, spurious signal suppression, and delay tracking. The extensibility of the design and digital data transport from antennas is considered. The interface with correlators using both the FX and XF topologies are discussed, noting that a distributed FX correlator performing the first stage of frequency channelization at the antenna dovetails well with the Digital Front-End requirements. The study includes a financial trade-off.

## Contents

| 1 | Intr          | oducti         | on                |                                                                            | 5                                |  |  |  |  |  |  |  |

|---|---------------|----------------|-------------------|----------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|--|

| 2 | $\mathbf{AL}$ | MA ne          | xt gener          | ation scientific goals and requirements                                    | 5                                |  |  |  |  |  |  |  |

| 3 | Dig           | ital Fro       | ont-End           | specification                                                              | 8                                |  |  |  |  |  |  |  |

|   | 3.1           |                |                   | $\operatorname{nts}^-$                                                     | 8                                |  |  |  |  |  |  |  |

|   |               | 3.1.1          |                   | Provisional Band-Dependent Performance Requirements                        | 8                                |  |  |  |  |  |  |  |

|   | 3.2           | ALMA           |                   | ients                                                                      | ç                                |  |  |  |  |  |  |  |

|   | J             | 3.2.1          |                   | Technical Requirements.                                                    | ç                                |  |  |  |  |  |  |  |

|   |               | 91 <b>2</b> 11 | 3.2.1.1           | Signal Dynamic Range, Passband IF variation and Quantization<br>Efficiency | 12                               |  |  |  |  |  |  |  |

|   |               |                | 3.2.1.2           | ALMA amplitude calibration sequence                                        | 14                               |  |  |  |  |  |  |  |

|   |               |                | 3.2.1.2 $3.2.1.3$ | Digital correction of phase/amplitude imbalance                            | 15                               |  |  |  |  |  |  |  |

|   |               |                | 3.2.1.3 $3.2.1.4$ | Continuous IF band coverage for line searches                              | 18                               |  |  |  |  |  |  |  |

|   |               | 2 0 0          |                   |                                                                            |                                  |  |  |  |  |  |  |  |

|   |               | 3.2.2          |                   | dequirements                                                               | 20                               |  |  |  |  |  |  |  |

|   |               | 3.2.3          |                   | S                                                                          | 20                               |  |  |  |  |  |  |  |

|   |               |                | 3.2.3.1           | Power                                                                      | 20                               |  |  |  |  |  |  |  |

|   |               |                | 3.2.3.2           | Cooling                                                                    | 20                               |  |  |  |  |  |  |  |

|   |               |                | 3.2.3.3           | Thermal                                                                    | 20                               |  |  |  |  |  |  |  |

|   |               |                | 3.2.3.4           | Mass                                                                       | 20                               |  |  |  |  |  |  |  |

|   |               | 3.2.4          |                   | Requirements                                                               | 21                               |  |  |  |  |  |  |  |

|   | 3.3           |                |                   | ormance of front-end designs similar to the current ALMA front-end         |                                  |  |  |  |  |  |  |  |

|   |               |                |                   |                                                                            | 22                               |  |  |  |  |  |  |  |

|   |               | 3.3.1          |                   | e (based on ALMA Band 8 2SB receiver compared with new SIS                 |                                  |  |  |  |  |  |  |  |

|   |               |                | generation        | on of SIS receivers)                                                       | 23                               |  |  |  |  |  |  |  |

|   |               |                | 3.3.1.1           | Band 8 cartridge IF variation in 4 GHz range                               | 23                               |  |  |  |  |  |  |  |

|   |               |                | 3.3.1.2           |                                                                            | 23                               |  |  |  |  |  |  |  |

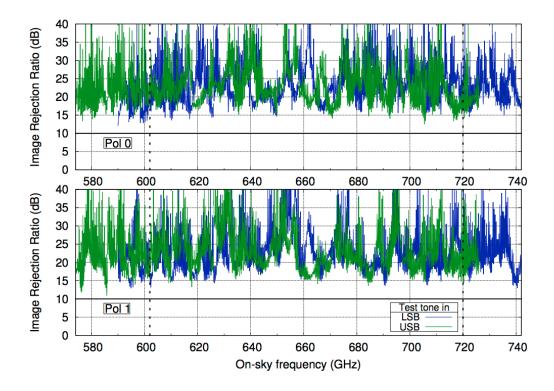

|   |               | 3.3.2          | Image Re          | ejection Ratio Analysis (based on 600-720 GHz 2SB receiver SEPIA660        |                                  |  |  |  |  |  |  |  |

|   |               |                |                   | ${ m X~telescope})$                                                        | 26                               |  |  |  |  |  |  |  |

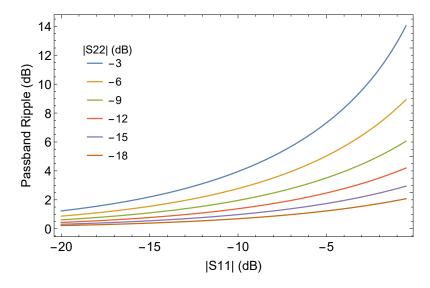

|   |               | 3.3.3          | IF pass b         | pand ripple analysis                                                       | 28                               |  |  |  |  |  |  |  |

|   |               |                | 3.3.3.1           | Ripple analysis                                                            | 28                               |  |  |  |  |  |  |  |

|   |               |                | 3.3.3.2           | SIS mixer output match estimates                                           | 30                               |  |  |  |  |  |  |  |

|   |               |                | 3.3.3.3           | System ripple mitigation                                                   | 31                               |  |  |  |  |  |  |  |

|   |               |                |                   |                                                                            |                                  |  |  |  |  |  |  |  |

| 4 | Dig           |                |                   |                                                                            | <b>3</b> 4                       |  |  |  |  |  |  |  |

|   | 4.1           | Quanti         |                   | v i o                                                                      | 34                               |  |  |  |  |  |  |  |

|   |               | 4.1.1          | -                 |                                                                            | 34                               |  |  |  |  |  |  |  |

|   |               | 4.1.2          |                   | f gain variations throughout the signal passband                           | 37                               |  |  |  |  |  |  |  |

|   | 4.2           | Overal         | l concept         |                                                                            | 40                               |  |  |  |  |  |  |  |

|   | 4.3           | Modul          | arity             |                                                                            | 42                               |  |  |  |  |  |  |  |

|   |               | 4.3.1          | Cost esti         | mate comparison for modular approach compared to existing ana-             |                                  |  |  |  |  |  |  |  |

|   |               |                | logue sw          | itch solution                                                              | 43                               |  |  |  |  |  |  |  |

|   | 4.4           | Digital        | Front-Er          | nd functions                                                               | <b>4</b> 4                       |  |  |  |  |  |  |  |

|   |               | 4.4.1          | Digital S         | ideband Correction                                                         | 44                               |  |  |  |  |  |  |  |

|   |               |                | 4.4.1.1           | Description of Digital Sideband Correction System                          | 44                               |  |  |  |  |  |  |  |

|   |               |                | 4.4.1.2           | Width of calibration channel for digital sideband correction ("first       |                                  |  |  |  |  |  |  |  |

|   |               |                |                   | F" engine channel)                                                         | 45                               |  |  |  |  |  |  |  |

|   |               |                | 4.4.1.3           | Experimental study of the channel width for the "First F" Engine           | 46                               |  |  |  |  |  |  |  |

|   |               |                | 4.4.1.4           | Analythical Analysis of the channel width for the "First F" engine.        |                                  |  |  |  |  |  |  |  |

|   |               |                |                   | Estimation for existing ALMA bands                                         | 46                               |  |  |  |  |  |  |  |

|   |               |                | 4.4.1.5           | Calibration source. Calibration speed and stability                        | 49                               |  |  |  |  |  |  |  |

|   |               |                | 4.4.1.6           | Conclusion, 10 years perspective                                           | 50                               |  |  |  |  |  |  |  |

|   |               | 4.4.2          |                   | ad equalization                                                            | 51                               |  |  |  |  |  |  |  |

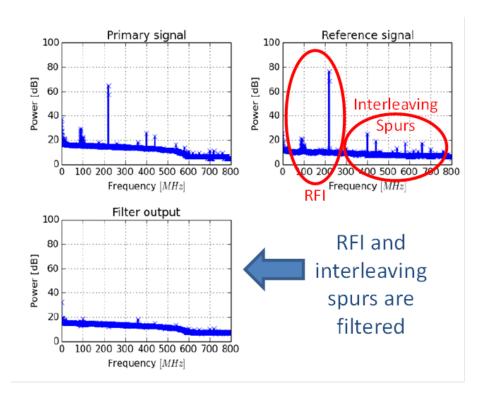

|   |               | 4.4.3          |                   | ing ADC Spurious removal by adaptive filtering                             | 52                               |  |  |  |  |  |  |  |

|   |               | 4.4.4          |                   | ng correlator (FX, XF)                                                     | 53                               |  |  |  |  |  |  |  |

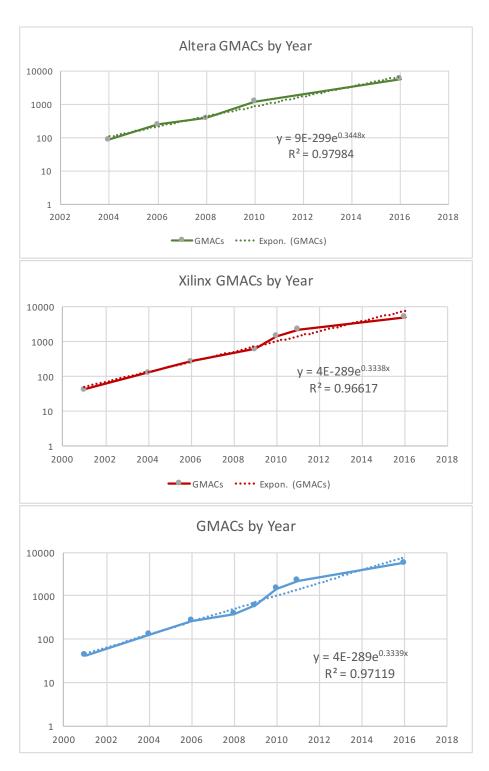

|   | 4.5           |                |                   | (FPGA) including calculation power and projection                          | 53                               |  |  |  |  |  |  |  |

|   | 4.6           |                |                   |                                                                            | 53                               |  |  |  |  |  |  |  |

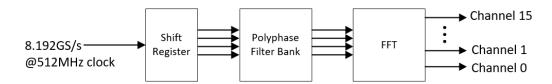

|   | 1.0           | Course         | uigida            | 2 CIGIII CII 2010 CI                                                       | Coarse F: digital channelization |  |  |  |  |  |  |  |

| 5 | Ana          | alogue processing and Digitization options                               | <b>55</b> |  |  |  |  |  |  |  |  |

|---|--------------|--------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|--|

|   | 5.1          | Analogue vs digital band switching                                       | 55        |  |  |  |  |  |  |  |  |

|   | 5.2          | Analogue vs digital baseband equalization                                | 55        |  |  |  |  |  |  |  |  |

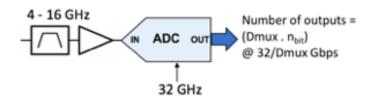

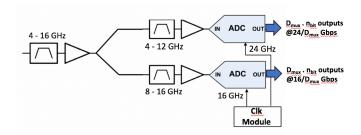

|   | 5.3          | ADC full band digitization, digitization, digitization options           | 55        |  |  |  |  |  |  |  |  |

|   |              | 5.3.1 General considerations                                             | 55        |  |  |  |  |  |  |  |  |

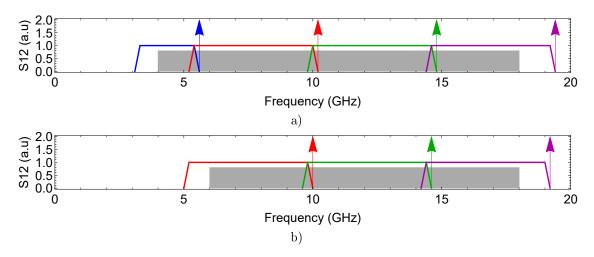

|   |              | 5.3.2 Current and future ALMA receiver IF ranges                         | 56        |  |  |  |  |  |  |  |  |

|   |              | 5.3.3 IF range digitization                                              | 56        |  |  |  |  |  |  |  |  |

|   |              | 5.3.4 Fastest COTS samplers                                              | 57        |  |  |  |  |  |  |  |  |

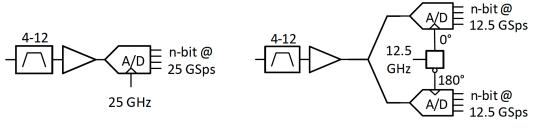

|   |              | 5.3.5 Design considerations for single- and dual-rate A-to-D conversion  | 59        |  |  |  |  |  |  |  |  |

|   |              | 5.3.5.1 Direct digitization                                              | 59        |  |  |  |  |  |  |  |  |

|   |              | 5.3.5.2 Dual-rate A-to-D conversion                                      | 60        |  |  |  |  |  |  |  |  |

|   |              | 5.3.5.3 Further technical considerations related to high bit rate        | 61        |  |  |  |  |  |  |  |  |

|   |              | 5.3.5.4 Brief comments on technology readiness and digitizer flexibility | 61        |  |  |  |  |  |  |  |  |

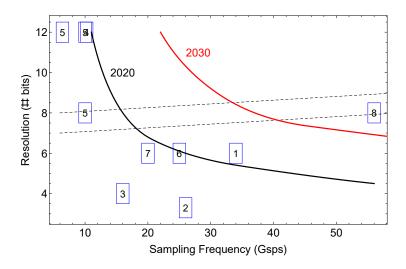

|   |              | 5.3.6 Forward look to future high speed ADCs                             | 61        |  |  |  |  |  |  |  |  |

|   |              | 5.3.7 Broad bandwidth digitization with many bits                        | 62        |  |  |  |  |  |  |  |  |

|   |              | 5.3.8 Data transfer between high speed ADCs and FPGAs                    | 63        |  |  |  |  |  |  |  |  |

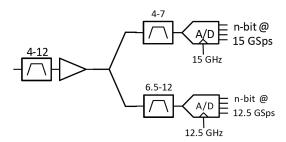

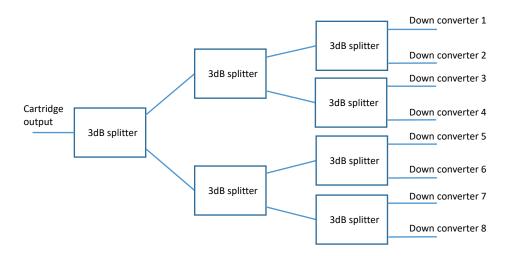

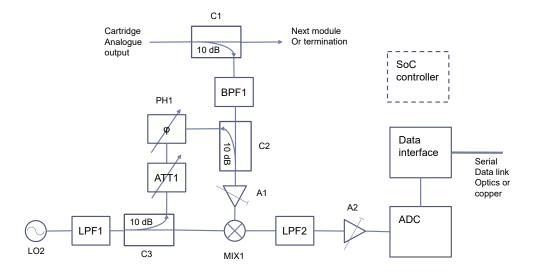

|   | 5.4          | Down-converter and high dynamic range digitization (multiple core ADC)   | 63        |  |  |  |  |  |  |  |  |

|   |              | 5.4.1 Down-converter                                                     | 63        |  |  |  |  |  |  |  |  |

|   |              | 5.4.2 High dynamic range digitization: multiple-core ADCs                | 65        |  |  |  |  |  |  |  |  |

|   |              |                                                                          |           |  |  |  |  |  |  |  |  |

| 6 | _            |                                                                          | 66        |  |  |  |  |  |  |  |  |

|   | 6.1          | 0                                                                        | 66        |  |  |  |  |  |  |  |  |

|   | 6.2          | Data transport physical layer                                            | 66        |  |  |  |  |  |  |  |  |

|   | 6.3          | Trade offs                                                               | 66        |  |  |  |  |  |  |  |  |

| 7 | D:a4         | twibuted Connelator & Dhased Armey and the DEE                           | 67        |  |  |  |  |  |  |  |  |

| • | 7.1          | • /                                                                      | 67        |  |  |  |  |  |  |  |  |

|   | $7.1 \\ 7.2$ | Two-stage channelization is required                                     | 68        |  |  |  |  |  |  |  |  |

|   | 1.4          |                                                                          | 69        |  |  |  |  |  |  |  |  |

|   | 7.3          | 7.2.1 Architectures Studied                                              |           |  |  |  |  |  |  |  |  |

|   | 7.4          |                                                                          |           |  |  |  |  |  |  |  |  |

|   | 7.5          | FX Facilitates Beam forming and VLBI Recording                           | 70<br>71  |  |  |  |  |  |  |  |  |

|   | 1.0          | 7.5.1 Beam forming requirements                                          | 71        |  |  |  |  |  |  |  |  |

|   |              | 7.5.2 VLBI Recorder requirements                                         | 72        |  |  |  |  |  |  |  |  |

|   |              | 1.0.2 YEDI 160001401 TOQUITOINOINS                                       |           |  |  |  |  |  |  |  |  |

| 8 | Ove          | erall trade offs and trends                                              | <b>73</b> |  |  |  |  |  |  |  |  |

|   | 8.1          | Digitizer trade off                                                      | 73        |  |  |  |  |  |  |  |  |

|   |              | 8.1.1 Key minimum requirements and their trends                          | 73        |  |  |  |  |  |  |  |  |

|   |              | 8.1.1.1 Dynamic range                                                    | 73        |  |  |  |  |  |  |  |  |

|   |              | 8.1.1.2 Digitization bandwidth and analog channels                       | 73        |  |  |  |  |  |  |  |  |

|   |              | 8.1.2 ADC technology trade off                                           | 74        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3 System digitizer solution trade off                                | 75        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.1 Bandwidth                                                        | 76        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.2 ENOBs or dynamic range                                           | 76        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.3 Power consumption                                                | 76        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.4 Cost                                                             | 76        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.5 System Complexity                                                | 77        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.6 Modularity                                                       | 77        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.7 Technical maturity                                               | 77        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.8 Spurious signals susceptibility                                  | 77        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.9 Availability                                                     | 77        |  |  |  |  |  |  |  |  |

|   |              | 8.1.3.10 Total ranking and conclusion                                    | 77        |  |  |  |  |  |  |  |  |

|   | 8.2          | Analogue vs. digital DFE signal distribution from cartridges             | 77        |  |  |  |  |  |  |  |  |

|   | 8.3          | Analogue vs. digital equalization                                        | 77        |  |  |  |  |  |  |  |  |

|   | 8.4          | Analogue vs. digital sideband rejection                                  | 77        |  |  |  |  |  |  |  |  |

|   | 8.5          | Data transfer trade off                                                  | 78        |  |  |  |  |  |  |  |  |

|   | 8.6          | "First F" engine                                                         | 78        |  |  |  |  |  |  |  |  |

|   | 8.7          | Frequency processing trade off                                           | 81        |  |  |  |  |  |  |  |  |

|   | 8.8          | Cost estimates                                                           |           |  |  |  |  |  |  |  |  |

|    |                       | 8.8.1   | Wide band digitizer option                                     | 81 |  |  |  |  |

|----|-----------------------|---------|----------------------------------------------------------------|----|--|--|--|--|

|    |                       | 8.8.2   | High dynamic range down converter/digitizer combination option | 81 |  |  |  |  |

|    |                       | 8.8.3   | High dynamic range down converter, RFSoC option                | 82 |  |  |  |  |

|    |                       | 8.8.4   | Analogue modifications cost analysis                           | 83 |  |  |  |  |

|    |                       | 8.8.5   | Cost summary table and comparison                              | 84 |  |  |  |  |

| 9  | Risl                  | k asses | $\mathbf{sment}$                                               | 85 |  |  |  |  |

|    |                       | 9.0.1   | Wide band digitizer option                                     | 85 |  |  |  |  |

|    |                       | 9.0.2   | High dynamic range down converter/digitizer                    | 85 |  |  |  |  |

|    |                       | 9.0.3   | High dynamic range down converter/digitizer, RFSoC solution    | 86 |  |  |  |  |

|    |                       | 9.0.4   | Analogue low pass band ripple option                           | 87 |  |  |  |  |

|    | 9.1                   | Risks   | summary                                                        | 88 |  |  |  |  |

| 10 | Sug                   | gestion | ns for future development                                      | 89 |  |  |  |  |

| 11 | Con                   | clusio  | n                                                              | 89 |  |  |  |  |

| 12 | .2 Acknowledgments 90 |         |                                                                |    |  |  |  |  |

### 1 Introduction

Vigorous and transformative investigation of the millimeter/submillimeter sky at high sensitivity and high resolution has benefited from the recent completion in 2013 of the Atacama Large Millimeter/submillimeter Array (ALMA)<sup>1</sup>, an effort of 22 countries. ALMA, a versatile interferometric observatory at 5000m elevation in the Atacama Desert of northern Chile, comprises sixty-six precision telescopes which may be arrayed over a 16 km extent on the high Chajnantor plain [1]. Owing to its large collecting area of approximately 6600 m<sup>2</sup> and its spectral grasp of 8 GHz of spectrum in dual polarizations within the 84-950 GHz range, ALMA provides astronomers with vastly improved spectroscopic sensitivity. Spatial resolutions of 20 milliarcsec were demonstrated recently, revealing a 1 au dark annulus in the TW Hya disk. Using ALMA's excellent imaging quality, dark substructure was found in the galaxy gravitationally lensing SDP.81.

From its conception it was realized that a program of upgrades would be necessary to keep ALMA at the forefront of technology during its projected 30-year operational lifetime. This process kicked-off even before the ALMA inauguration with projects launched to add capabilities that, due to funding constraints, were descoped during the construction phase, such as the band 1 receiver covering 35-50 GHz and a phasing capability that enables ALMA to take part in global Very Long Baseline Interferometry (VLBI) arrays. This process will continue with the addition of band 2 receivers which will complete the originally envisaged frequency coverage from 35-950 GHz and with a new study for the next ALMA correlator providing very high frequency resolution, and versatility<sup>2</sup> several upgrade studies to increase the frequency resolution and bandwidth of digital system and proposals under discussion to add band 2 which will complete the originally envisaged frequency coverage from 35-950 GHz.

Given that the work to complete ALMA would soon be done, attention turned to the question of how best to use the available ALMA upgrade development funds in order to further extend its scientific capabilities in the period up to 2030. To this end the ALMA Science Advisory Committee (ASAC) set up a group to establish a set of scientific priorities for ALMA in the next decade. Their report was further elaborated and combined with a survey of technology status by a cross-disciplinary working group which culminated the release of the ALMA 2030 Roadmap document (see next section).

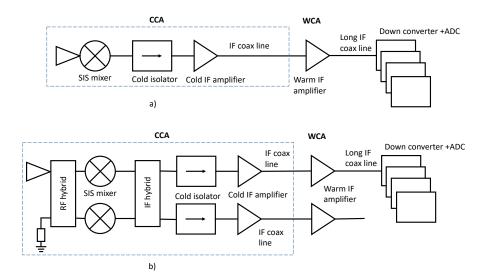

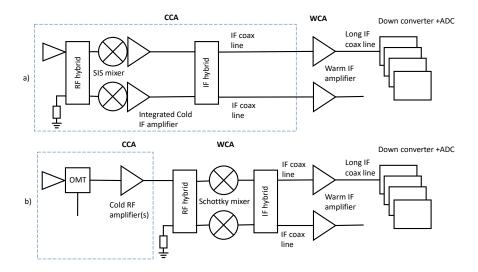

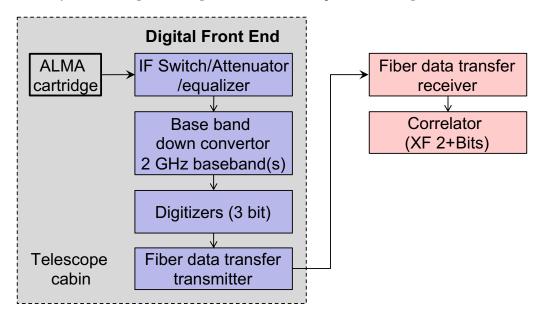

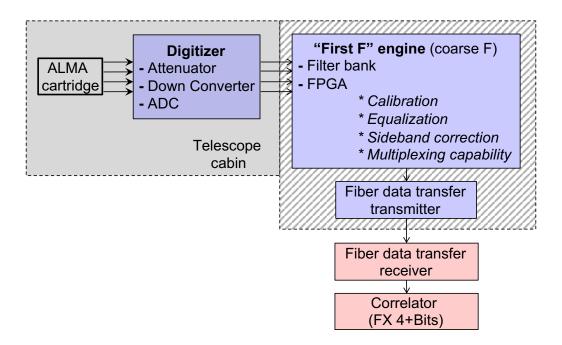

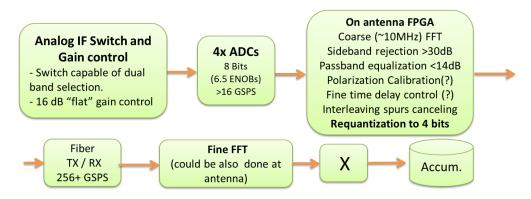

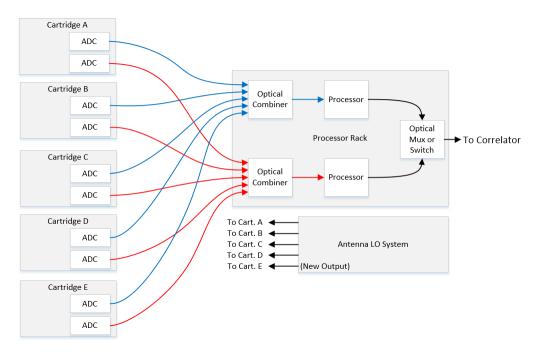

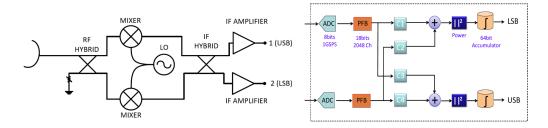

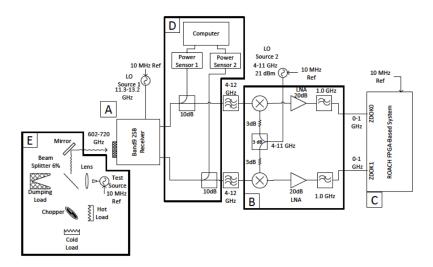

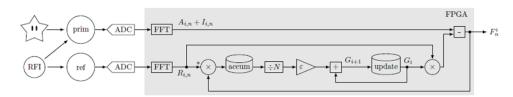

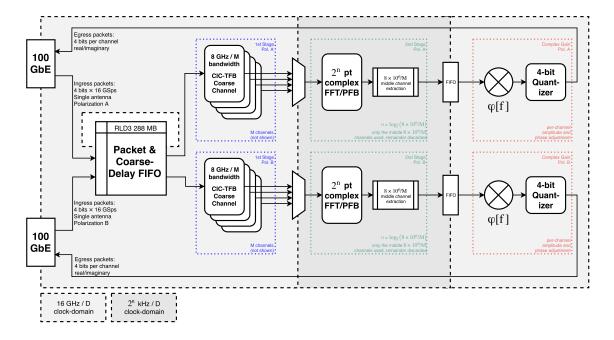

The "ALMA Digital Front-End: Configuration Study" was proposed as part of the ESO ALMA technology study program and established a Digital Front-end Working Group (DFWG) comprising experts from institutes representing all ALMA regions, including NRAO, JAO, ESO, NAOJ, NOVA/Kapteyn astronomical, University of Chile, Bordeaux University, MPIfR and Harvard Smithsonian. The goal of this work is to identify and evaluate options for optimizing the front-end – back-end architecture using modern digital signal processing techniques. The systems under study would provide the core functions of digitization of the IF band, pass band equalization, fine delay tracking, initial frequency channelization and data transfer to the ALMA correlator. Such a digital processing system could also provide functions such as digital phase and amplitude balance calibration for sideband separating receivers; flexible selection of spectral windows, potentially from different bands or multipixel arrays; removal of polarization leakage terms.

This Final Study report discusses ALMA scientific and technical requirements for ALMA system in the context of the improvements a digital FE processing system could provide. An analysis of the impact of improved calibration accuracy on ALMA observations is presented. The report presents a survey of technologies and trends which can be used in the time span of 10 years (mid term) to create DFE system. Finally, a trade off between several architectures is presented, including a discussion of interface options with different correlator architectures, and a possible technical development roadmap is proposed.

### 2 ALMA next generation scientific goals and requirements

ALMA is currently the most sensitive millimeter/submillimeter observatory in operation, and has yielded over 1000 publications in its first five years of operation. However, without upgrades ALMA

<sup>&</sup>lt;sup>1</sup> ALMA is a partnership of ESO (representing its member states), NSF (USA) and NINS (Japan), together with NRC (Canada), NSC and ASIAA (Taiwan), and KASI (Republic of Korea), in cooperation with the Republic of Chile. The Joint ALMA Observatory is operated by ESO, AUI/NRAO and NAOJ.

<sup>&</sup>lt;sup>2</sup>The approved correlator upgrade to increase the frequency resolution by a factor of 8 has recently been terminated.

runs the risk of not maintaining its position of field dominance. To this end an ALMA Development Working Group (J. Carpenter, D. Iono, L. Testi, N. Whyborn, A. Wootten, and N. Evans; hereafter ADWG) was formed and charged with proposing a science driven vision for ALMA development over the medium to long term (5-15 years) that was prioritized and consistent with the anticipated development budget. The ADWG developed an ALMA Development Roadmap that was approved by the ALMA Board in November 2017, and published as public ALMA Memo No. 612 [2].

The ADWG proposed the following fundamental science drivers for ALMA over the next decade: **Origins of Galaxies**

Trace the cosmic evolution of key elements from the first galaxies (z>10) through the peak of star formation (z=2-4) by detecting their cooling lines, both atomic ([CII], [OIII]) and molecular (CO), and dust continuum, at a rate of 1-2 galaxies per hour.

#### **Origins of Chemical Complexity**

Trace the evolution from simple to complex organic molecules through the process of star and planet formation down to solar system scales ( $\sim 10\text{-}100$  au) by performing full-band frequency scans at a rate of 2-4 protostars per day.

#### **Origins of Planets**

Image protoplanetary disks in nearby (150 pc) star formation regions to resolve the Earth forming zone ( $\sim 1$  au) in the dust continuum at wavelengths shorter than 1mm, enabling detection of the tidal gaps and inner holes created by planets undergoing formation.

Achieving these ambitious goals is currently impossible even with the outstanding capabilities of the current ALMA array; they require maintaining or increase in line sensitivity in addition to bandwidth broadening and increasing the number of spectral channels available. Therefore, the ADWG recommended that the top development priority, based on scientific merit and technical feasibility, is broadening the ALMA receiver IF bandwidth by at least a factor two while maintaining sensitivity; and to upgrade the associated electronics and correlator to: provide more spectral channels, eliminate the aliasing gaps, and reduce the loss due to quantization. The ADWG also recommended improving the scientific functionality of the ALMA Science Archive and supported the study of a range of future upgrade options that it considered fell outside the scope of the period up to 2030.

The new science goals can be achieved with the upgrades proposed in The ALMA Development Roadmap, upgrades that would make ALMA even more powerful and keep it at the forefront of astronomy by continuing to produce transformational science and enabling fundamental advances in our understanding of the universe for the decades to come.

The ALMA Digital Front-end Working Group (DFWG) work directly addresses a key part of the Roadmap primary development recommendation by identifying suitable upgrade options for more than doubling the digitized IF bandwidth at increased bit depth. Additionally, techniques such as digital sideband separation are effective ways to improve ALMA's capabilities as we discuss below. A suitably designed flexible Digital Front-End (DFE) could support future upgrades such as multibeam receivers or dual-frequency operation if those are prioritized beyond the 2030 timeframe considered in the Roadmap.

In order to guide the priorities of the DFWG, we consider the types of observations requested for Cycle 6 (private communication). Of the 1870 proposals received, 351 required mosaics (19%), most of which are on Nyquist sampled hexagonally-packed arrays of pointings. 578 Cycle 6 proposals (31%) requested observations requiring more than one frequency tuning, of which 230 only requested multiple tunings in the same band, and 428 requested tunings in 2 or more different bands. Since all ALMA observations would benefit from improved sensitivity, we consider the DFE potential impact on sensitivity to be the highest priority for the DFWG.

There is a consensus that to achieve these goals several ALMA system improvements are needed where this study can have significant impact:

- Significantly improve instantaneous bandwidth and bandwidth coverage which requires to at least double up to perhaps quadruple the instantaneous digitization bandwidth from the current 4 GHz per sideband (8 GHz per polarization) to 8 GHz per sideband or more by utilizing possible modular expansion approach.

- Improving sensitivity by increasing digitization bit depth to 5 ENOB at least, thus allowing to improve current theoretical correlation efficiency of 86% up to 99%.

- Provide a modular platform for front-end improvements by utilizing flexible FPGA DSP and a modular architecture (including data transport) to support any future front-end

receiver improvement needs with the least impact on the rest of the system. Modular platform is aimed at providing a cost effective expansion of the capabilities. This is highly desirable in the view of possible new scientific insights which may need update of such capabilities as well as consideration of focal plane arrays capability in long run. At least, this should support later extension of front-end IF bandwidth coverage by installing additional modules with appropriate capabilities which will work together with previous generation. This will provide significant cost savings.

The followings sections will present trade of studies and a roadmap proposal on what will be possible with appropriate development direction in the 10+ years timescale.

### 3 Digital Front-End specification

#### 3.1 New Requirements

In this section we reflect on ALMA technical requirements in 10+ years perspective, which are the most relevant for the DFE study.

Table 1 lists the key requirements that the DFWG considers should be modified and which are consistent with the recommendations of the ALMA 2030 Roadmap. Where applicable the table lists the current requirement and the proposed new requirement.

Table 1: Summary of New Requirements.

| Parameters              | Old Req $\#$                    | New Value                                |

|-------------------------|---------------------------------|------------------------------------------|

| Receiver IF bandwidth   | 4 GHz (IF 4-8 GHz for 2SB or    | At least 8 GHz (IF 4-12 GHz); with       |

| (per sideband per po-   | 4-12 GHz for 1SB and DSB)       | a goal of 16 GHz (IF 4-20 GHz)           |

| larization)             |                                 |                                          |

| Continuous IF cover-    | Anti-aliasing filters result in | The processed IF bandwidth shall         |

| age                     | the loss of about 125 MHz       | cover at least a 3:1 frequency ratio     |

|                         | for each 2 GHz baseband         | with no gaps or lost coverage at the     |

|                         | resulting in a total usable     | IF band edges                            |

|                         | instantaneous bandwidth of      |                                          |

|                         | $\sim 7.5 \text{ GHz}$          |                                          |

| Front-end Sideband      | >10 dB for 90% of the IF        | > 20 dB with a goal of $>$ 30 dB under   |

| Rejection Ratio         | range (SSB and 2SB) $> 7$ dB    | all conditions                           |

|                         | over 100% of the IF range       |                                          |

|                         | (SSB and 2SB)                   |                                          |

| Digital Base band cali- | Analogue equalization only,     | True digital base band correction        |

| bration                 | limited to 2 GHz sub-bands      | with 10 MHz channel spacing *            |

| Correlator bit depth    | 2 and 3                         | full 4 bits for all frequency resolution |

| and transport           |                                 | modes/ full IF band                      |

| Analogue inputs         | 2 polarisations, 2 sidebands,   | 2 x 2 x 10 with the possibility to       |

|                         | 10 frequency bands              | extend                                   |

| Digital Processing      | 2-pols x 4 basebands            | 2-pols basebands                         |

| channels                |                                 |                                          |

| Compatibility           |                                 | DFE concept should be able to sup-       |

|                         |                                 | port operations with current ALMA        |

|                         |                                 | XF correlator, ALMA compact ar-          |

|                         |                                 | ray FX correlator, possible future       |

|                         |                                 | FFX correlator upgrade by adapting       |

|                         |                                 | FPGa software only.                      |

| Flexibility             |                                 | Where practical the design shall         |

|                         |                                 | support upgrades to increase the         |

|                         |                                 | number of IF channels and/or in-         |

|                         |                                 | creased IF bandwidth and/or mul-         |

|                         |                                 | tiplexing.                               |

<sup>\*</sup> In current ALMA ACA (compact array) as well as main correlator has already implemented similar procedure where the channelized scalings applied in the correlator before re-quantizations (BLC FDM modes per 62 MHz sub-band, ACA per-channel after FFT). These have similarities to aspects of what is proposed, although they only work with 3-bit sampled input rather than proposed 5..6.

#### 3.1.1 ALMA Provisional Band-Dependent Performance Requirements.

The provisional requirements that are proposed to be enforced for new cartridge designs from now until the science requirements are updated in 2019 are shown in table 2. This table represents the minimum upgrade necessary to be consistent with the 2030 Roadmap but does not include additional improvements which are expected to be technically feasible within the 2030 scope. The ALMA DFE specifications and architecture should at least support these IF bandwidths but

should aim to be flexible enough to support the goal IF range listed in Table 1, should front-end and correlator technology make those feasible.

| Band<br>No. | Freq. Range,<br>GHz | Max. Rcvr.<br>Temp., K<br>(100% of band) | Max. Rcvr.<br>Temp.,K<br>(80% of band) | BW per<br>polarization<br>in IF range,<br>GHz | Front-End<br>Type | IF Range,<br>GHz <sup>f</sup> |

|-------------|---------------------|------------------------------------------|----------------------------------------|-----------------------------------------------|-------------------|-------------------------------|

| 1           | 35–50               | 32                                       | 25                                     | 8, HFET                                       | USB               | 4-12                          |

| 2           | 67–95               | 47                                       | 30                                     | 16, HFET                                      | 2SB               | 4-12                          |

| 3           | 84–116              | 60 <sup>a</sup>                          | 37 <sup>a</sup>                        | 16, SIS                                       | 2SB               | 4-12                          |

| 4           | 125-163             | 82                                       | 51                                     | 16, SIS                                       | 2SB               | 4-12                          |

| 5           | 163-211             | 105                                      | 65                                     | 16, SIS                                       | 2SB               | 4-12                          |

| 6           | 211-275             | 136                                      | 83                                     | 16, SIS                                       | 2SB               | 4-12                          |

| 7           | 275-373             | 219 <sup>b</sup>                         | 147                                    | 16, SIS                                       | 2SB               | 4–12 <sup>e</sup>             |

| 8           | 385-500             | 292                                      | 196                                    | 16, SIS                                       | 2SB               | 4–12 <sup>e</sup>             |

| 9           | 602-720             | 261 <sup>c</sup>                         | 175 <sup>c</sup>                       | 16, SIS                                       | 2SB               | 4–12 <sup>e</sup>             |

| 10          | 787–950             | 344 <sup>c</sup>                         | 230 <sup>c d</sup>                     | 8, SIS                                        | DSB               | 4-12 <sup>e</sup>             |

Table 2: Band-Dependent Requirements.

#### Notes:

#### 3.2 ALMA requirements

In this section we propose the ALMA front-end/back-end/correlator requirements relevant for the near-term. Achieving or improving upon these requirements should be feasible with the proposed DFE system architecture and for this document these are considered as **Minimum system requirements**. These include specifications from the ALMA front-end including bandwidth upgrade, and rationale for few key specification, such as required dynamic range, required full equivalent number of bits (ENOB) of digitizer (SINAD and white noise).

#### 3.2.1 Critical Technical Requirements.

Table 3 shows technical requirements relevant for the digital front-end – back-end study. These are based on the recommendations in the ALMA Development Roadmap [2] and other inputs. The requirement identification code (# column) indicates to which array the requirement is applicable: "M" refers to the EU (European) and NA (North American) Antennas and/or to the 64-Antennas Correlator.

"T" refers to the Mitsubishi 12 m (PM) antennas or any other 12 m antenna used in the Total Power (TP) antenna array.

"7" refers to the Atacama Compact Array (ACA) 7 m antennas and correlator.

"T/7" refers to the ACA Correlator and both TP and 7 m arrays.

A blank code indicates that the requirement applies to all arrays.

The abbreviations "R", "T" and "T\*" in parentheses in the parameter column specify the verification method to be used (see ALMA Project Documentation Standards, ALMA-80.02.00.00-003-G-STD).

<sup>&</sup>lt;sup>a</sup> Noise temperature requirement shown reverted to original version.

$<sup>^{</sup>m b}$  Relaxed noise temperature, <300 K, for the RF frequency range 370-373 GHz.

This relaxation would likely be removed for a future design

<sup>&</sup>lt;sup>c</sup> DSB noise temperature. Future band 9 and 10 designs would likely be 2SB.

$<sup>^{\</sup>rm d}$  230 K over 80% of a reduced frequency range (787-905 GHz).

<sup>&</sup>lt;sup>e</sup> There is interest to increase the IF bandwidth, but the details are not yet decided.

<sup>&</sup>lt;sup>f</sup> At least 3:1 frequency ratio, nominally  $4.0-12.0~\mathrm{GHz}$  +/- 5.%

Table 3: Summary Table of Critical Technical Requirements.

| Parameter                                             | $\mathbb{R}$ eq | # | Proposed Value                                                                                                                                                                             | Sci<br># |

|-------------------------------------------------------|-----------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Signal Dynamic range (T*)                             | 227.1           |   | The system shall be designed to accommodate variations in the total power signal level of 4 dB during an observation while meeting the quantization noise requirement #521                 | ,,,      |

|                                                       | 227.2           |   | The system shall be designed to accommodate an increase in the total power signal level of up to 12 dB during an observation with no more than 25% loss in sensitivity                     |          |

|                                                       | 227.3           |   | The system shall have at least 16 dB of gain adjustment to compensate for differences of in IF power level between bands, different hardware (serial numbers), and at different FE tunings |          |

| 1st Mixer Sideband<br>Ratio (T)                       | 231             |   | > 20 dB suppression over 100% of the IF frequency range, SSB and 2SB (with a goal of > 30 dB)                                                                                              |          |

|                                                       |                 |   | < 3 dB difference across 80% of the combined<br>IF and LO frequency ranges, DSB                                                                                                            |          |

| Front-End: IF output (R)                              | 234             |   | All 2SB FE systems shall output to the BE both sidebands simultaneously                                                                                                                    |          |

| Freq range, 1st IF (T*)                               | 240             |   | The processed IF bandwidth shall cover at least a 3:1 frequency ratio, nominally $4.0-12.0~\mathrm{GHz}\pm5\%$ , with no gaps or lost coverage at the IF band edges                        |          |

| Total Instantaneous<br>Bandwidth (T*)                 | 250             |   | $> 16 \text{ GHz} \pm 5\% \text{ per polarization (2SB)}$<br>$> 8 \text{ GHz} \pm 5\% \text{ per polarization (SSB & DSB)}$                                                                |          |

| Gain Stability: .05-<br>100 sec (T*)                  | 261             |   | Allan Standard Deviation (ASD) $< 1.0 * 10^{-3}$ on time scales of 0.05 to 100 seconds; applies to all antennas                                                                            | 300      |

| Gain Stability: 100 to 300 seconds (T*)               | 262             |   | $ASD < 3.0 * 10^{-3}$ on time scales of 100 to 300 seconds; applies to all antennas                                                                                                        | 300      |

| Total Power Gain Stability (T*)                       | 263             | Т | $ASD < 4.0 * 10^{-4}$ at time scales of 0.05 to 1.0 sec for the 4 antennas used for total power observations                                                                               | 305      |

| Polarization: Complex gain Stability (T)              | 264             |   | a) < 0.01 in amplitude and b) < 0.4 degrees of phase for ASD time periods 0.05 to 300 sec                                                                                                  | 320      |

| Baseband filter: stop-<br>band response (T*)          | 270             |   | Deleted, replaced by new requirement #280                                                                                                                                                  |          |

| Baseband filter: pass-<br>band response (T*)          | 271             |   | Deleted, replaced by new requirement #280                                                                                                                                                  |          |

| Bandpass Shape: gain v.s. freq; wide band (T)         | 272             |   | Gain variation (p-p) across the whole IF band, due to all system components, under any tuning shall be less than 10 dB                                                                     |          |

| Bandpass Stability:<br>spectral gain v.s. time<br>(T) | 273.1           |   | 1 sec: Temporal change in bandpass gain or shape of auto correlation. < -40 dB over 1 second                                                                                               | 70       |

| Bandpass Stability:<br>spectral gain v.s. time<br>(T) | 273.2           |   | 1 hr: Temporal change in bandpass gain or shape of cross correlation < -30 dB over 3600 seconds                                                                                            | 70       |

| System spurious responses (T*)                        | 280             |   | Spurious responses in the IF processing system shall<br>be suppressed by at least 40 dB with respect to the<br>wanted in-band response                                                     | 70       |

Table 3: Summary Table of Critical Technical Requirements.

| Parameter                                                            | $egin{array}{c c} \mathbf{Req} & \# \end{array}$ | # Proposed Value                                                                                                                                    | Sci       |

|----------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Broad-band Spurious<br>Signal – Incoherent<br>among antennas (T)     | 292                                              | a) IF power in incoherent spurious signals shall be < -10 dB per unit bandwidth relative to the nominal system noise power per unit bandwidth.      | 71        |

|                                                                      |                                                  | b) stability of the incoherent spurious signals shall be < -20 dB per unit bandwidth relative to the nominal system noise power per unit bandwidth. |           |

| Broad-band Spurious<br>Signal – Coherent<br>among antennas (T)       | 293                                              | < -17 dB averaged over the continuum bandwidth,<br>before suppression by LO offsetting or phase switch-<br>ing;                                     | 80        |

|                                                                      |                                                  | In those cases where spur suppression is not effective, the requirement is $<$ -47 dB                                                               |           |

| Narrow-band Spurious Signal – Coherent among all antennas (T)        | 295.1                                            | < -28 dB before interferometric spur suppression<br>(spur signal power relative to the system noise<br>power in a 1 MHz bandwidth)                  | 70        |

|                                                                      |                                                  | In those cases where spur suppression is not effective, the requirement is $<$ -58 dB                                                               |           |

| Narrow-band Spurious<br>Signal – Spur ampli-<br>tude stability – In- | 295.2                                            | < -32 dB rms of a random component, and $<$ - 56 dB constant difference component                                                                   | 70        |

| coherent or coherent among antennas (T)                              |                                                  | (the difference of the spur signal power in two switching states, relative to the system noise power, both in a 1 MHz bandwidth)                    |           |

| Spurious Signal: Sta-                                                | 297                                              | < -48 dB rms of a random component, and                                                                                                             | 70,<br>80 |

| bility of spur ampli-<br>tude integrated over<br>2GHz bandwidth of   |                                                  | < -72 dB constant difference component                                                                                                              | 00        |

| Total Power Detector (T)                                             |                                                  | (the difference in two switching states of the aggregate spur signal power over the 2 GHz baseband, relative to the system noise power)             |           |

| Digital Signal Transmission (T)                                      | 311                                              | The cable delay in each DTS should remain constant within ±8ns for at least 2 weeks.                                                                |           |

| Digital Signal Trans-<br>mission – Bit Error<br>Rate (T*)            | 312                                              | The Bit Error Rate (BER) for each DTS should be better than 10-6.                                                                                   |           |

| Sampling clock: fine delay steps (R)                                 | 323                                              | Variable phase for fine delay, $< 1/16$ sample accuracy.                                                                                            |           |

| Sampling clock: common to all antennas (R)                           | 324                                              | Common to all channels at an antenna.                                                                                                               |           |

| Sampling clock: syn-<br>chronization to corre-<br>lator (T)          | 325                                              | Delay changes inserted at both the BE and correlator shall be synchronized to better than 500 $\mu$ s.                                              |           |

| Detection and cor-<br>relation                                       |                                                  |                                                                                                                                                     |           |

| Total power detectors (R)                                            | 510                                              | Total power detectors shall be provided for each IF channel for engineering monitoring and science purposes                                         |           |

| Total power detectors: frequency range (R)                           | 510.1                                            | The engineering detectors shall cover the complete IF range (requirement 240)                                                                       |           |

Table 3: Summary Table of Critical Technical Requirements.

| Parameter                                    | Req<br># | # | Proposed Value                                                                                                                                                                                                                                                                         | Sci<br># |

|----------------------------------------------|----------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                              | 510.2    |   | The science detectors upper and lower frequency range shall be configurable in increments of 0.1 GHz or less within the IF range (#240)                                                                                                                                                |          |

| Total power detectors: accuracy (T*)         | 511      |   | Accuracy 1% of full scale (after linearity correction) and shall meet the stability requirements #261 – #263                                                                                                                                                                           |          |

| Total power detectors:<br>Full scale         | 511.1    |   | The total power detectors full scale IF power level shall be $+13$ dB relative to the nominal sky power level                                                                                                                                                                          |          |

| Total power detectors: sampling interval (R) | 512      |   | Sampling interval for science detectors shall be configurable over the range 0.5 msec to 10 s at $>$ 99 % efficiency                                                                                                                                                                   |          |

| Total power detectors:  Dynamic range        | 513      |   | The total power detectors shall have a dynamic range $> 13~\mathrm{dB}$                                                                                                                                                                                                                |          |

| Quantization resolution (R)                  | 521      |   | The loss of sensitivity at any frequency on the IF passband due to quantization and digital processing in the signal chain shall be less than 4% for all conditions of passband power variation (gain flatness) and allowed input signal level changes                                 | 190      |

| System Restart: calibration (T)              | 618      |   | It shall be possible to perform warm restart (soft resets) or power cycles of equipment at the module, sub-system and system level, including the Full System Restart, without recalibrating the telescope beyond those calibrations carried out during normal observation activities. |          |

| System Restart: time (T)                     | 619      |   | It shall be possible to restart any part of the system, including the full system (supposing all receivers are operational i.e. at nominal cooled temperature), in less than 15 minutes                                                                                                |          |

| WVR: Correction error & rate (T)             | 622      | M | Path length correction error (rms) $\delta L < (0.01w + 10) \mu m$ , with a sampling rate $< 1$ Hz.                                                                                                                                                                                    | 290      |

In the following subsections the most critical requirements, requiring a trade-off will be discussed.

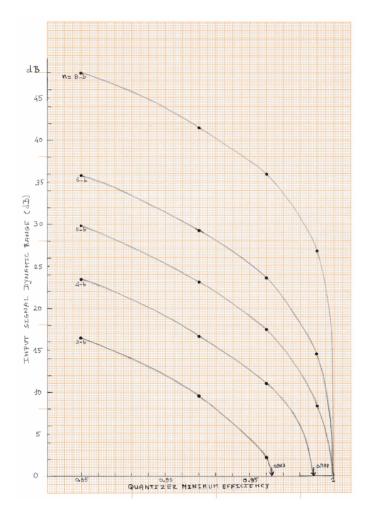

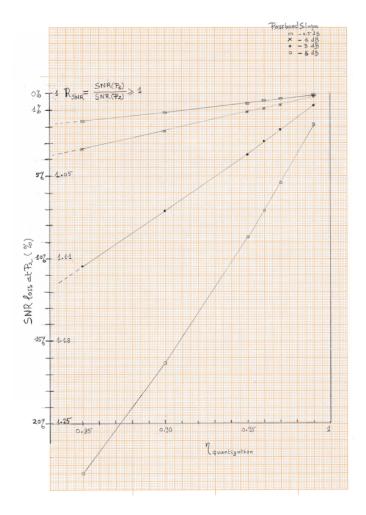

#### 3.2.1.1 Signal Dynamic Range, Passband IF variation and Quantization Efficiency

There are three critical parameters that drive the required ENOB versus sample-rate trade-off in the selection of samplers and the choice of IF architecture, these are: Signal Dynamic Range, Passband IF variation and Quantization Efficiency. These are dealt with in the following subsections.

#### Signal Dynamic Range

This is the range of signal power levels that the IF chain has to cope with and can be broken down to two parts:

- Power level changes during the observing sequence, for example due to sky opacity changes from weather or changes in elevation, and gain drift in the receiver system.

- Power level changes that occur from observation to observation (e.g. due to LO1 changes), from band to band, and from front-end to front-end.

The first part always has to be accommodated by the ADC regardless of architecture in order to keep the analog IF signal processing path to be unchanged during the complete duration of

a calibration and science target observation sequence. This is because any practical circuit for modifying the overall gain of the IF system will introduce a frequency dependent change in the complex gain of the system thus giving rise to both phase and amplitude calibration errors.

However, the variations from the second part can be accommodated by adjusting the IF system gain immediately prior to starting the calibration at a new frequency or configuration thus reducing the dynamic range that the samplers need to cope with.

Table 4 gives the sources of power level changes during an observation for three cases: non-solar science target observing, atmosphere calibration sequence, solar observing. It is not considered feasible to compensate for these variations in power level by using adjustable attenuators or gain elements in the IF system in front of the samplers.

| Source                   | Dynamic          | Required     | Notes                                  |

|--------------------------|------------------|--------------|----------------------------------------|

|                          | $\mathbf{range}$ | quantization |                                        |

|                          |                  | efficiency   |                                        |

| Sky brightness changes   | 3 dB             | 96%          | Neil Phillips (private communication). |

| IF level setting error   | 1 dB             | 96%          | Combination of IF attenuator resolu-   |

|                          |                  |              | tion and setting error.                |

| Sub-total: science tar-  | 4 dB             | 96%          | System Requirements #227.1 & #521      |

| gets                     |                  |              |                                        |

| AtmCal calibration se-   | 12 dB            | 75%          | Hot load versus cold sky (see Table 7  |

| quence                   |                  |              | for the band dependent values).        |

| IF level setting error   | 1 dB             | 75%          | Combination of IF attenuator resolu-   |

|                          |                  |              | tion and setting error.                |

| Sub-total: flux calibra- | 13 dB            | 75%          | System Requirement #227.2              |

| tion                     |                  |              |                                        |

| Solar observations       | 12 dB            | 90%          | TBC Receiver detuning or optical at-   |

|                          |                  |              | tenuator.                              |

| IF level setting error   | 1 dB             | 90%          | Combination of IF attenuator resolu-   |

|                          |                  |              | tion and setting error.                |

| Sub-total: solar ob-     | 11 dB            | 75%          | Provisional value, TBC.                |

| serving                  |                  |              |                                        |

Table 4: IF power level dynamic range and quantization efficiency requirements during an observation. The first part of the table applies while observing the science targets (except the Sun); the second part applies during the atmospheric and flux calibration cycle; and the third part applies during solar observations.

Table 5 gives the power level changes between observations. These changes may be compensated with an adjustable attenuator in the IF system before the sampler, i.e. to reduce the range of signal levels the sampler has to operate with. If an adjustable attenuator is **not** used to compensate for these level changes, then the sampler has to accommodate these changes in addition to those listed in Table 4 with the stated minimum quantization efficiency applicable to each case.

| ĺ | Source              | Dynamic | Required           | Notes                      |

|---|---------------------|---------|--------------------|----------------------------|

|   |                     | range   | ${f quantization}$ |                            |

|   |                     |         | efficiency         |                            |

|   | Cartridge variation | 16 dB   | 96%                | System Requirement #227.3. |

Table 5: IF power level changes between observations. These level changes arise due to differences in net signal gain between different LO tunings for the same receiver, between different receivers of the same band and between different receiver bands.

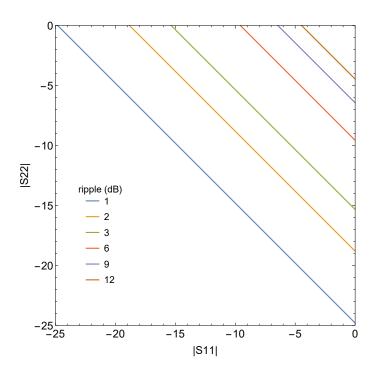

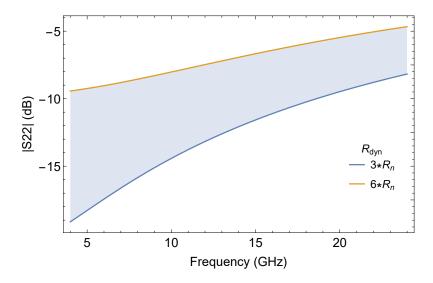

#### Passband IF variation

This is the signal level variation across the passband due to ripple, gain-slopes etc. The relevant bandwidth for this discussion is that which pertains to the sampler baseband input. The proposed requirements are listed in Table 6.

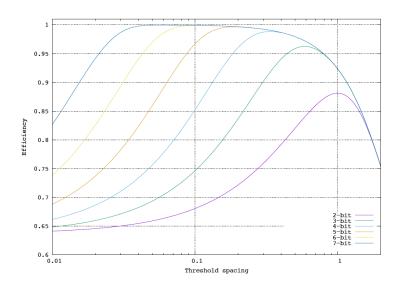

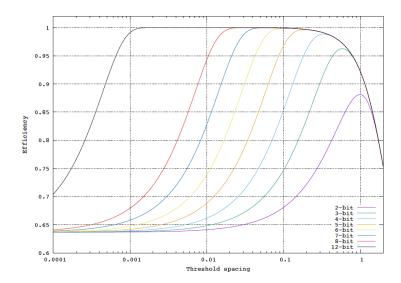

#### Quantization Efficiency

The relatively coarse quantization employed by samplers typically used for radio astronomy intro-

| Case                                | Value | Notes                                     |

|-------------------------------------|-------|-------------------------------------------|

| Gain variation across whole IF band | 13 dB | Unchanged $(#272)$                        |

| Gain variation across baseband      | 8 dB  | Based on the existing requirement of 8 dB |

|                                     |       | across 2 GHz (#271)                       |

Table 6: IF level variations allowed across the IF passband. The first applies to variations allowed across the whole of the IF band. The second applies to variations which occur within the baseband of the ADC (this only applies to architectures that split the IF band into multiple bands each feeding an ADC).

duces errors in the representation of the incoming signal that can be viewed as additional noise. Quantization efficiency is the relative loss in signal-to-noise ratio resulting from the introduction of this noise in the quantization process. This leads to the concept of quantization efficiency. For the analysis that follows quantization noise is defined as 1 - quantization efficiency. The level of this quantization efficiency and therefore noise relative to the wanted signal depends on the number of sampler levels and the signal level relative to the sampler level spacing. Quantization efficiency is discussed in detail in Section 4.1.1.

For the quasi-random signals with a Gaussian distribution being digitised in ALMA, the quantization noise is spread uniformly across the Nyquist band. This implies that the signal to noise ratio across the baseband is proportional to the variation in signal level across the passband at the sampler input. This implies that the signal to quantization noise ratio in troughs of the passband signal level is degraded by the depth relative to the average power density or, typically, half of the peak to peak variation across the baseband passband: 8 dB peak to peak variation degrade the SNR by 4 dB.

#### 3.2.1.2 ALMA amplitude calibration sequence

Part of the standard calibration sequence for ALMA observations measures the power levels detected while looking at the sky, an ambient temperature black-body load (typically at 16 C) and a heated black-body load at a temperature of  $\tilde{8}5$  C. The IF power level is first set to the level that maximizes sensitivity while observing the science target. Thereafter the receiver looks at the ambient and hot loads. The resulting changes in signal level during this cycle depend on the effective sky temperature, the opacity, the receiver noise temperature and the temperatures of the two calibration loads.

Table 7 shows the measured values of receiver and system noise temperatures at the 10th percentile, and the dynamic range between observing the hot load and cold sky at the 90th percentile, for bands 3-10 (the values for bands 1 & 2 are projected values based on expected receiver performance and sky transmission). This shows that IF level changes of up to slightly more than 10dB may be expected during the calibration sequence.

| Band # | ${f Trec} \ /{f K}$ | Tsys $/\mathbf{K}$ | Dynamic range /dB |

|--------|---------------------|--------------------|-------------------|

| 1      | 25                  | 37                 | 10.2              |

| 2      | 30                  | 45                 | 9.3               |

| 3      | 30                  | 50                 | 8.9               |

| 4      | 33                  | 53                 | 8.7               |

| 5      | 28                  | 63                 | 7.9               |

| 6      | 34                  | 66                 | 7.7               |

| 7      | 50                  | 107                | 5.8               |

| 8      | 90                  | 260                | 2.4               |

| 9      | 77                  | 320                | 1.3               |

| 10     | 158                 | 470                | 0.4               |

Table 7: Empirical band dependent receiver noise temperature and system temperature at the 10th percentile as measured in 2017 & 2018. (Bands 1 & 2 are theoretical values). The quoted noise temperatures are SSB values for all bands except 9 & 10 which are DSB values. The fourth column shows the 90th percentile dynamic range required for atmospheric calibration using the standard ALMA calibration loads at temperatures of 358 K & 290 K.

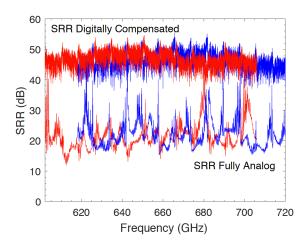

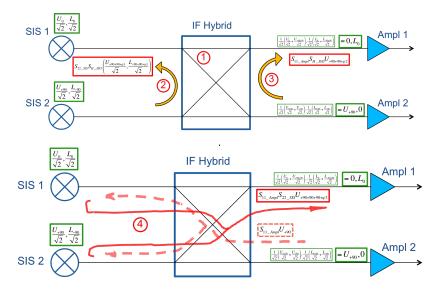

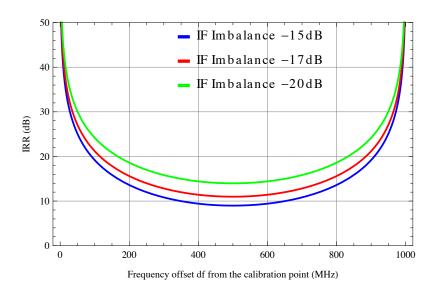

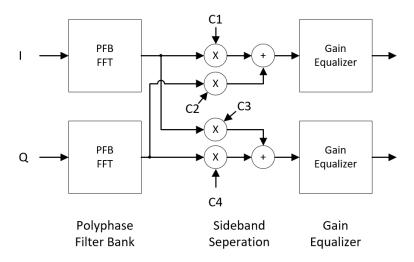

#### 3.2.1.3 Digital correction of phase/amplitude imbalance

Digital correction of phase & amplitude imbalance in 2SB mixers should allow much improved image suppression, especially when high dynamic range digitizers are being employed. Laboratory demonstrations have shown that image rejection ratios up to 50 dB are possible with an 8 ENOBs digitized 2SB system, see Section 4.4.1. The main advantage of sideband separation at DFE is utilizing full noise bandwidth and dynamic range of the digitizer allows to suppress not only lines in the image band, correlated between ALMA antennas, but also sky noise and optical component noise arriving at a single antenna much like the analogue quadrature sideband separating scheme as already employed for ALMA bands 3 through 8. We would like to estimate the impact of the digital sideband suppression system on the system noise temperature level over the existing analogue 2SB ALMA cartridges. The existing analogue sideband ratio is taken to be  $SBR = 7 \, dB$  as worst case and  $SBR = 12 \, dB$  as typical case. It is recognized that SBR for ALMA cartridges is function of both LO and IF frequency and in many cases may exceed 15 dB for some parts of IF band at given LO frequency, however it is not possible to reach such performance for all IF band and all LO frequencies for existing ALMA 2SB cartridges.

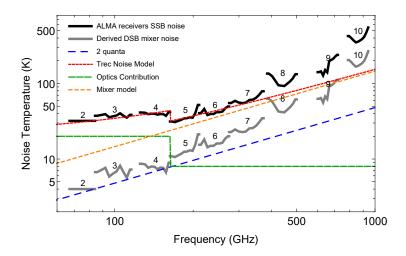

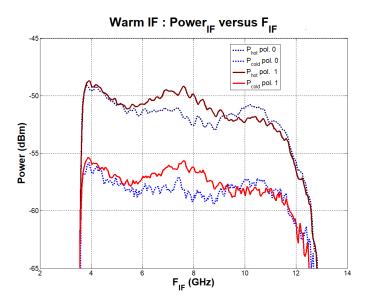

Let us consider the measured ALMA front-end noise temperature  $T_{SSB}$  distribution as shown in figure 1 as black line. expressed in DSB noise temperature. The  $T_{SSB}$  for ALMA band 9,10 is obtained by doubling the DSB values. In order to investigate trend of the noise temperature we build the noise model of the system. First we estimate the SIS mixers SSB noise temperature

$$T_{SSB,mix} = 2\left(\frac{T_{IF} * f}{400 * 10^9} + 2 * \frac{hf}{2k}\right),$$

(1)

where f is signal frequency; h and k Planck and Boltzmann constants respectively,  $\frac{hf}{2k}$  is photon energy with quantum noise is taken as double value,  $\frac{400*10^9}{f}$  represents model of SIS mixer gain, while IF system noise temperature  $T_{IF}$  is taken as 10 K. The calculated  $T_{SSB,mxi}$  is shown in figure 2 in dashed line labeled "Mixer model" (orange color). This line clearly describes the trend in measured  $T_{SSB}$  for band 5-9 and for bands 5-7 it also describes the trend of noise temperature within the band, indicating that these bands are already close to intrinsic limit of the mixer noise. For the top part of band 9 and especially band 10 the deviation is larger and can be attributed to increased losses in superconducting materials at these frequency. Notably, bands 2-4 depart significantly from general model trend as if there is a fixed noise contribution on top of  $T_{SSB,mix}$ . This fixed contribution can be explained by an increased noise coming from warm optics, which only exists in band 1-4 in ALMA system. When this optics contribution  $T_{opt}$  is included, we can create final model for  $T_{SSB}$ :

$$T_{SSB,model} = T_{SSB,mix} + T_{opt}, (2)$$

where  $T_{SSB,mix}$  is given by (1) and  $T_{opt}$  has been estimated from the fit to a measured  $T_{SSB}$ . A simple estimate for  $T_{opt}$  of a fixed value of 20 K for bands 1-4 and 8 K for bands 5-10 was sufficient to obtain a fit  $T_{SSB,model}$  labeled "Trec Noise Model" in the figure 1. The optics contribution  $T_{opt}$  is shown in the same figure by dashed line. For higher bands, the optical contribution comes mainly through cryostat window and LO insertion coupler and is small relative to receiver noise temperature, while for lower bands relatively large contribution comes from warm optics elements and their spill-over.

Finally, if we know the approximation of optical part of noise temperature  $T_{opt}$  we can calculate intrinsic underlying mixer DSB noise temperature  $T_{DSB,mix}$ , which together with sideband ratio  $SBR=7~\mathrm{dB}$  or  $SBR=12~\mathrm{dB}$  results in measured noise temperature according to the following equation:

$$T_{DSB,mix} = 0.5 \left( T_{SSB} - T_{opt} \left( 1 + \frac{1}{SBR} \right) \right). \tag{3}$$

Calculated  $T_{DSB,mix}$  is shown in figure 1 with label "Derived DSB mixer noise" and it only depends on assumption of  $T_{opt}$ , sideband ratio SBR and measured  $T_{SSB}$ . Calculated values closely follow the quantum limit, shown in the same figure for reference, for lower frequencies and slightly departs from it above 400 GHz.

Now it is possible to vary SBR and calculate its impact for front-end noise temperature  $T_{rec,model}$  using following equation:

$$T_{rec,model} = 2 * T_{DSB,mix} + T_{opt} \left( 1 + \frac{1}{SBR} \right). \tag{4}$$

Figure 1: Model results describing measured performance of ALMA front end receiving system. See explanation in text

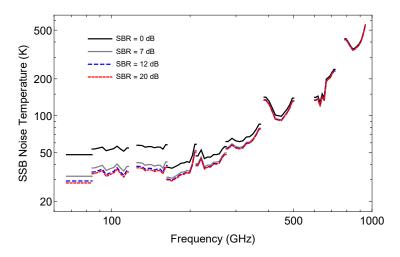

Figure 2: Front-end receiver noise temperature estimated for different sideband ratios SBR

Estimate for  $T_{rec,model}$  are shown in figure 2. The SBR=0 dB curve corresponds virtual DSB case and is only applicable to ALMA band 9,10 in current system. The SBR=7 dB replicates measured  $T_{SSB}$  by definition of model set up. Finally, SBR=20 dB presents receiver noise with a digital sideband separation of 20 dB. Significant relative noise change can be stated for low frequency bands 2-4, while the influence of SBR diminishes at higher frequency bands. Since observing efficiency is proportional to  $T_{noise}^2$  one can already estimate impact of as large as 25 % in integration times for lower frequency bands relative to SBR=7 dB and 12 % relative to SBR=12 dB.

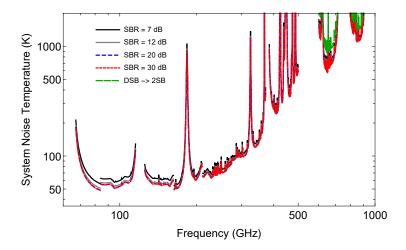

For estimating full impact the developed model is used together with atmospheric data for zenith brightness  $T_a$  and zenith opacity  $\alpha_a$  for 25th percentile in ALMA site. The resulting system noise temperature  $T_{SSB,sys}$  including optics and atmosphere can be calculated using the following equation:

$$T_{SSB,sys} = \left(T_{rec,model} + T_a \left(1 + \frac{1}{SBR}\right)\right) / \alpha_a / 0.8,\tag{5}$$

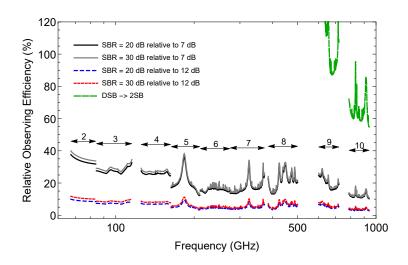

where we assume that aperture efficiency of the system is 0.8 and system spill-over is coupled to cold sky. The resulting estimates are present in figure 3. Here again SBR = 0 dB corresponds to DSB mixers in ALMA band 9,10. Significant gain in system noise temperature for SBR = 20 dB relative to SBR = 12 dB (current system) now can be observed both for low frequencies due to relatively large optical contribution and for high frequencies due to relatively small atmospheric transmission and large zenith atmospheric brightness. The observing efficiency gain vs SBR is presented in figure 4 and expressed as decrease of observing time relative to current SBR = 12 dB

Figure 3: Calculated SSB system noise temperature  $T_{SSB,sys}$  for 25th percentile atmospheric conditions at the ALMA site and different sideband ratios SBR

system and worst case SBR = 7 dB system.

Observing time gain of more than 5..10 % can be obtained for all bands, with maximum up to 40 % for band 2-3. ALMA band 1 is not considered throughout the modeling as this is pure SSB system, which can not be improved digitally. Relative gain of implementing 2SB band 9,10 systems is also shown in figure 4 as SBR = 0 dB relative to SBR = 7 dB, demonstrating gains well above 40 % for spectral line cases, based on noise consideration only. Increasing SBR further than 20 dB does not demonstrate significant gain in observing time by the above model.

The data in figures 3 and 4 is based on a moving average of sky transmission/brightness with a window size of approximately 1 GHz window in frequency. This masks another aspect to be considered: the presence of strong telluric lines in the image sideband. These lines are not correlated between antennas and their effect on  $T_{sys}$  can not be suppressed in the correlator by LO switching. The telluric lines can produce antenna temperatures up to 200K so image suppression of 20dB is needed to keep their contribution to  $T_{sys}$  below 5% in the lower bands and ideally it should be  $> 25~{\rm dB}$ .

The following items listed below are noted here for completeness, they are discussed in more detail in Section 4.4.1 of this document:

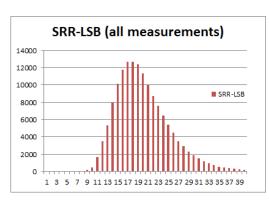

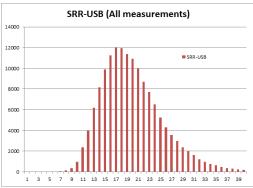

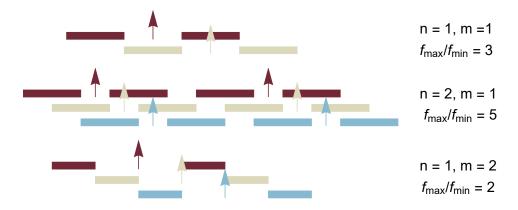

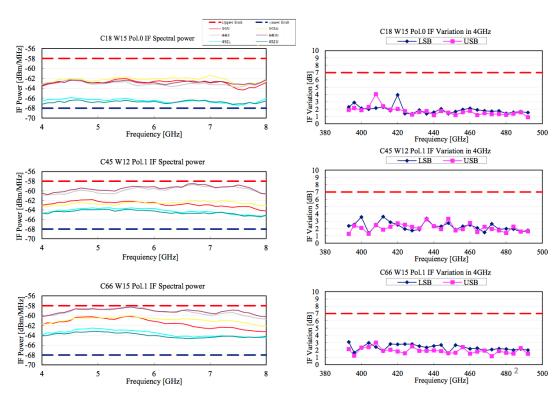

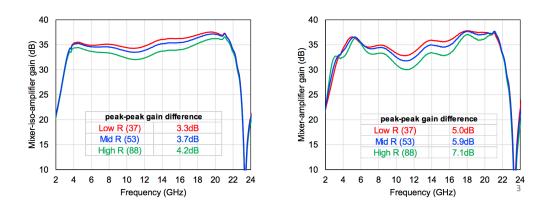

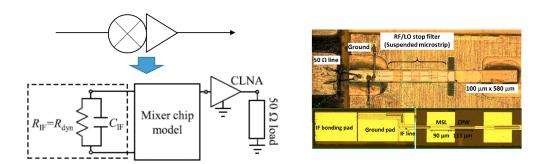

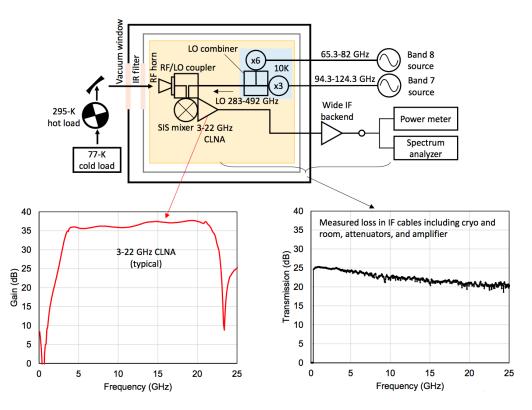

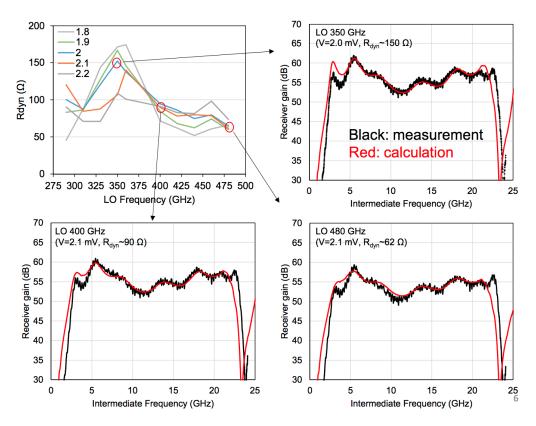

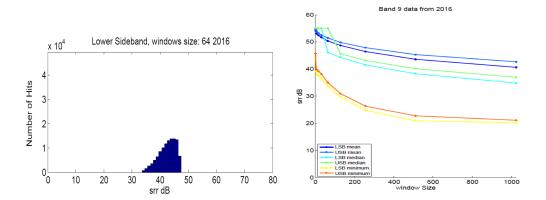

• Time overhead to calibrate out imbalance needs to be considered: it has been demonstrated that proposed system has enough resources to do that with margin