## RTC-Workshop Dec 5<sup>th</sup>, 2012

## **Present Microgate RTCs and perspectives**

R. Biasi

Microgate

# Past and present RTCs applications at Microgate

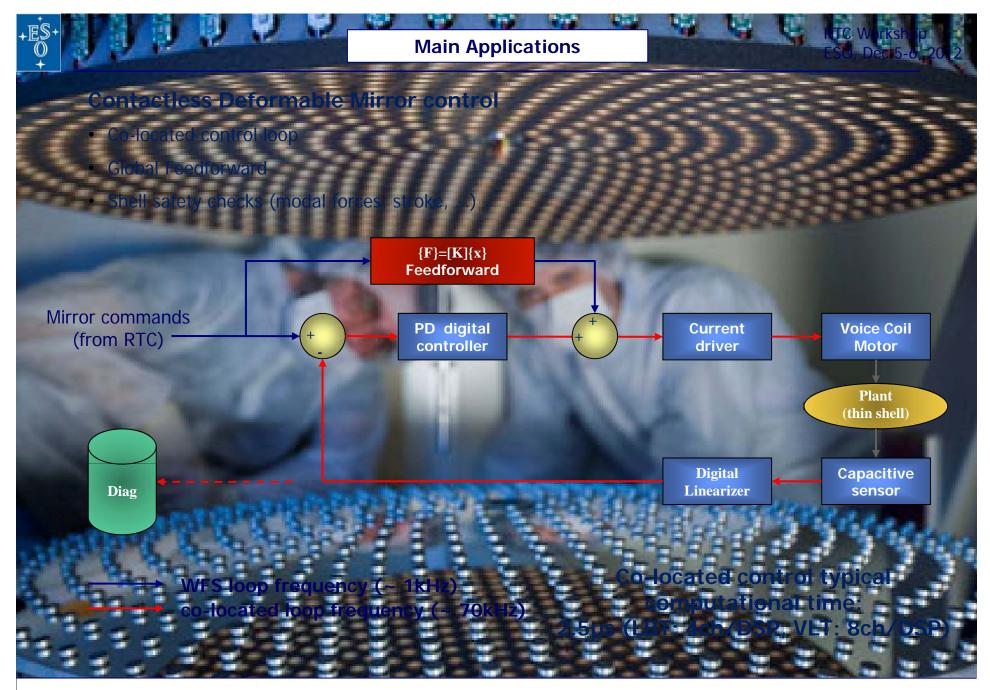

- Real time control of AO correctors

- Real-time reconstructors

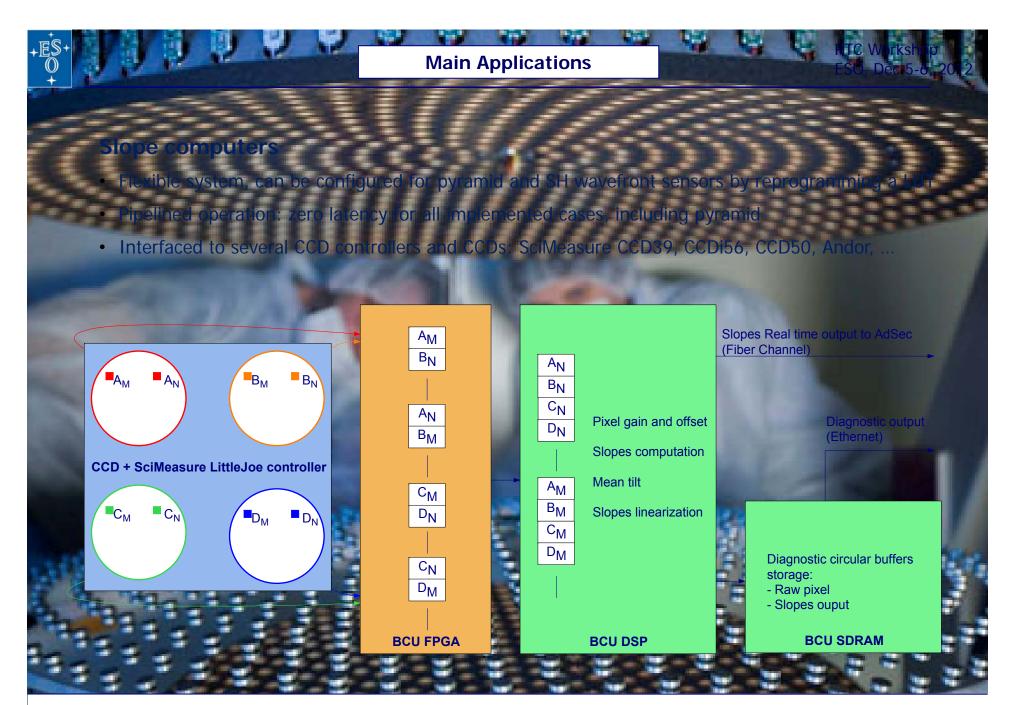

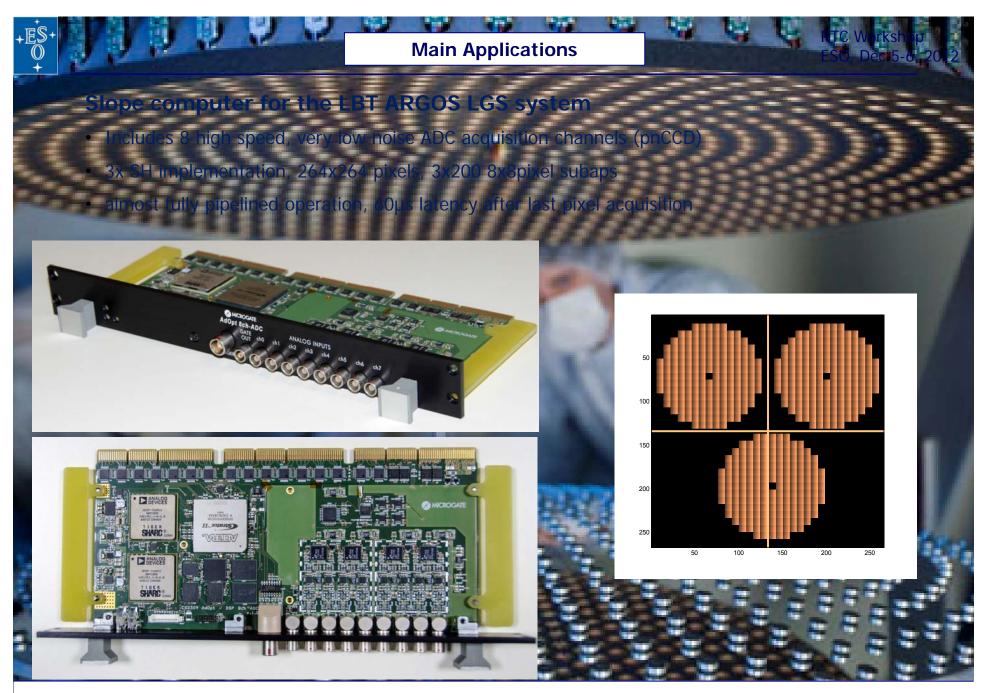

- Slope computers

- Software aspects

- Lessons learned

- Future perspectives

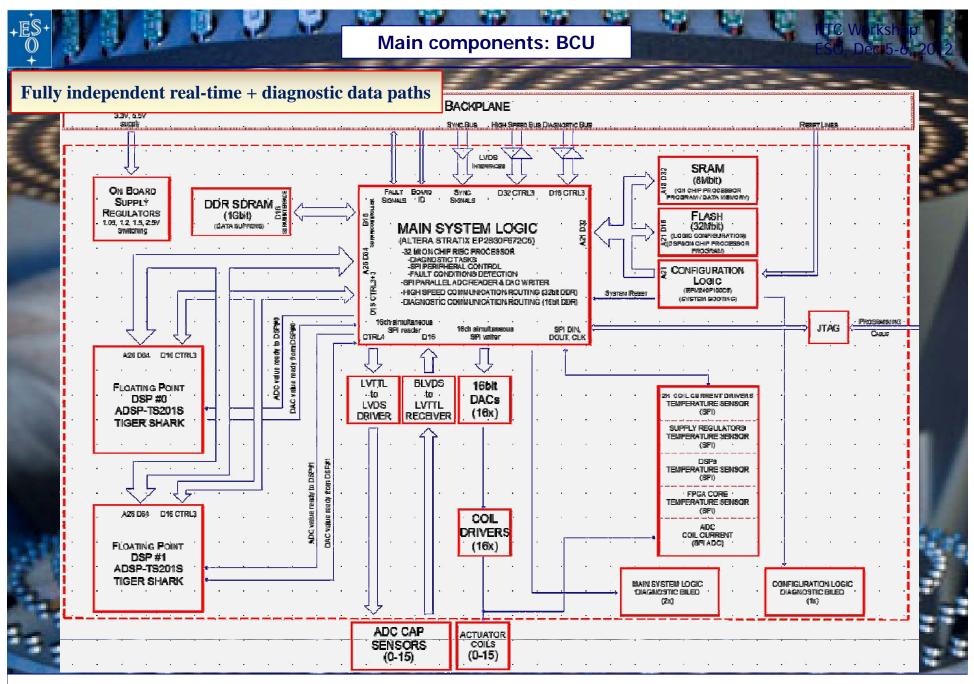

#### MMAC/s floating point sustained

- ICA ter seemless interfacing to various protocols and sensors (S-FPDP, SciMeasure, Andor, Xine

- PGA performs also hardware anceleration + housekeeping (NIOS)

- Gigabit Ethernet interface (copper or liber) for diagnostic

- 4x fiber modules up to 2.5 Gbit/s each (FiberChannel, S-FPDP) for real time communication

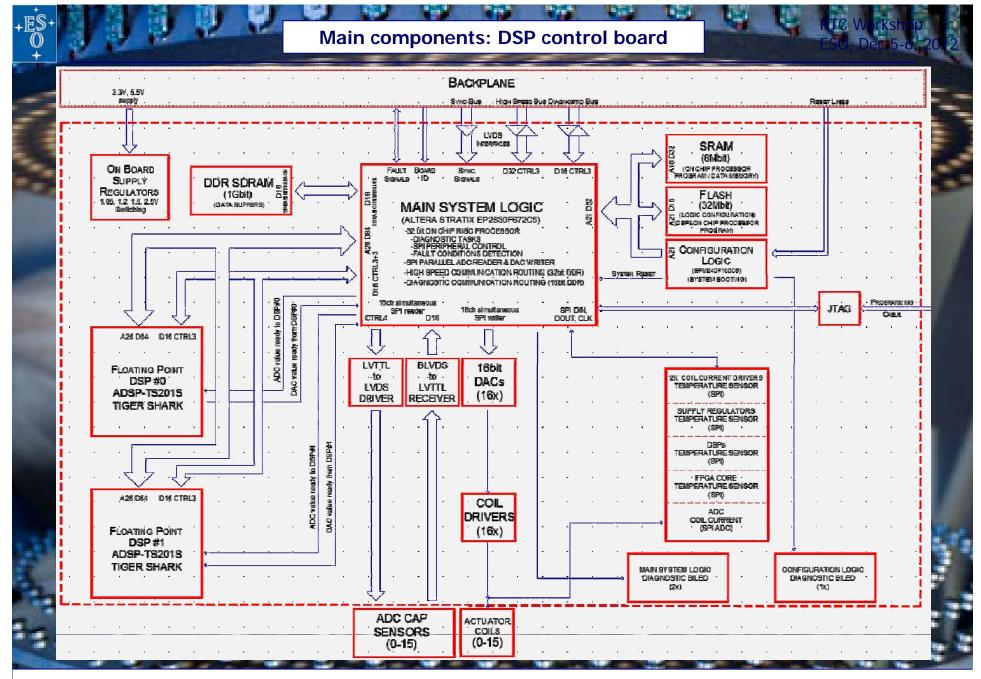

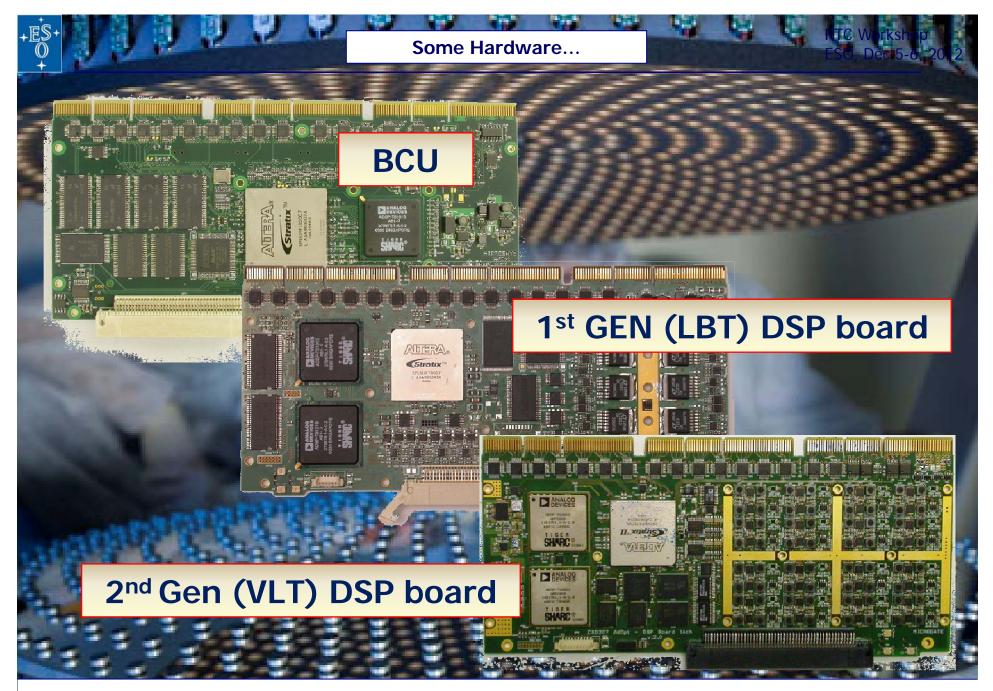

#### **DSP board**

Backplane

- 1 GMAC/s floating point sustained (LBT 84 boards, 84 GMAC/s) AD DSP TS101

- FPGA for data routing (DMA from/to DSPs, bulk memory access, NIOS embedded controller)

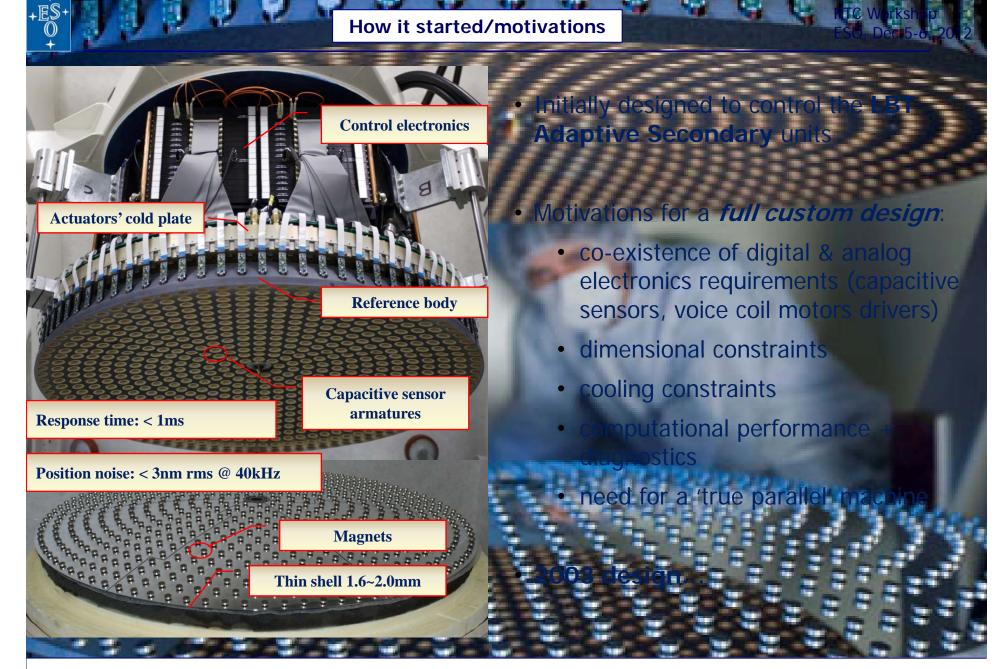

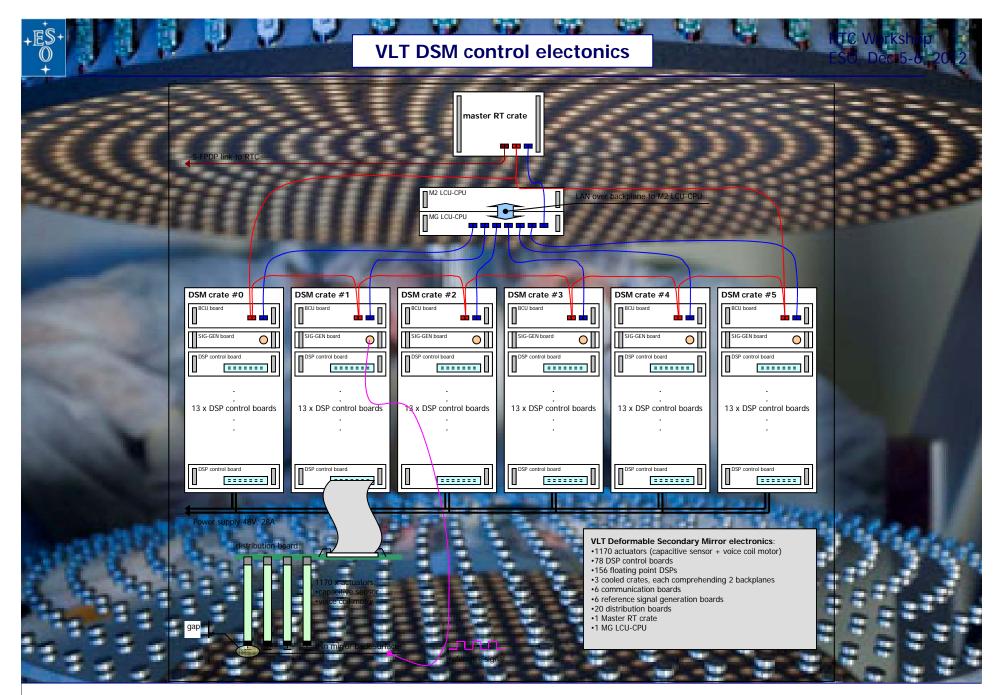

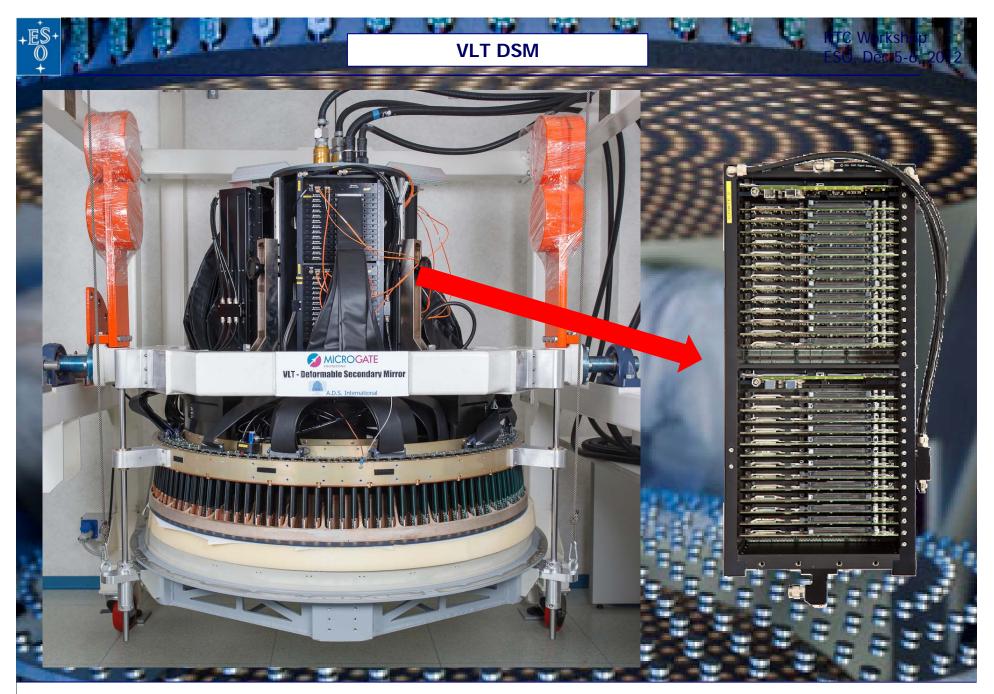

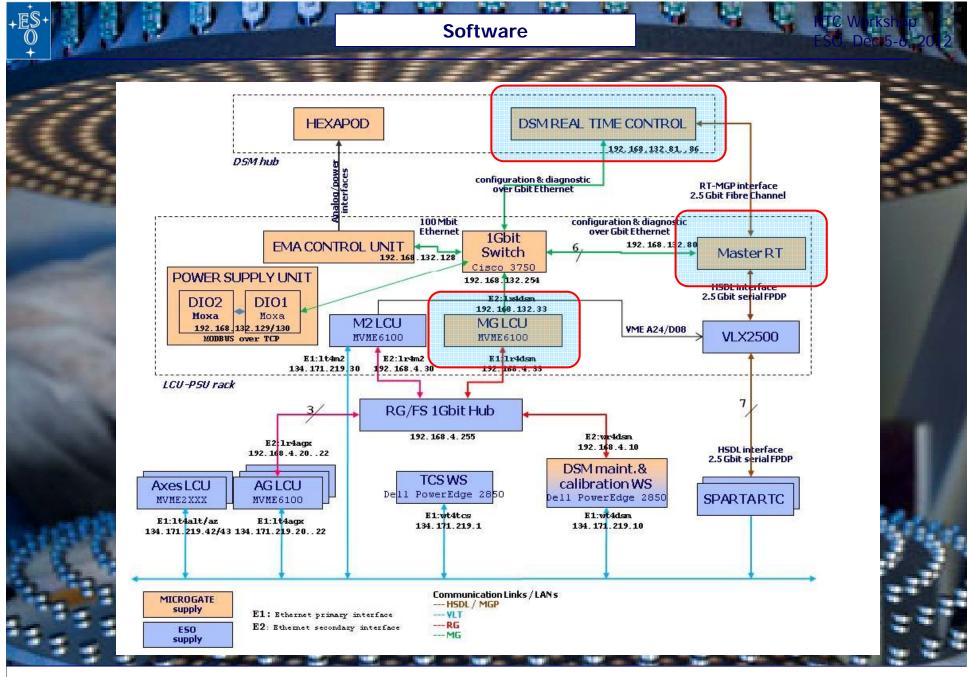

#### Gen 2 DSP board (VLT DSM)

- 2 GMAC/s floating point sustained (VLT: 78 boards, 156 GMAC/s) AD DSP TS201

- FPGA for data routing (DMA from/to DSPs, bulk memory access, NIOS embedded controller)

- 16 controlled channels, capacitive sensors + voice coil motor

#### I time reconstructor

122

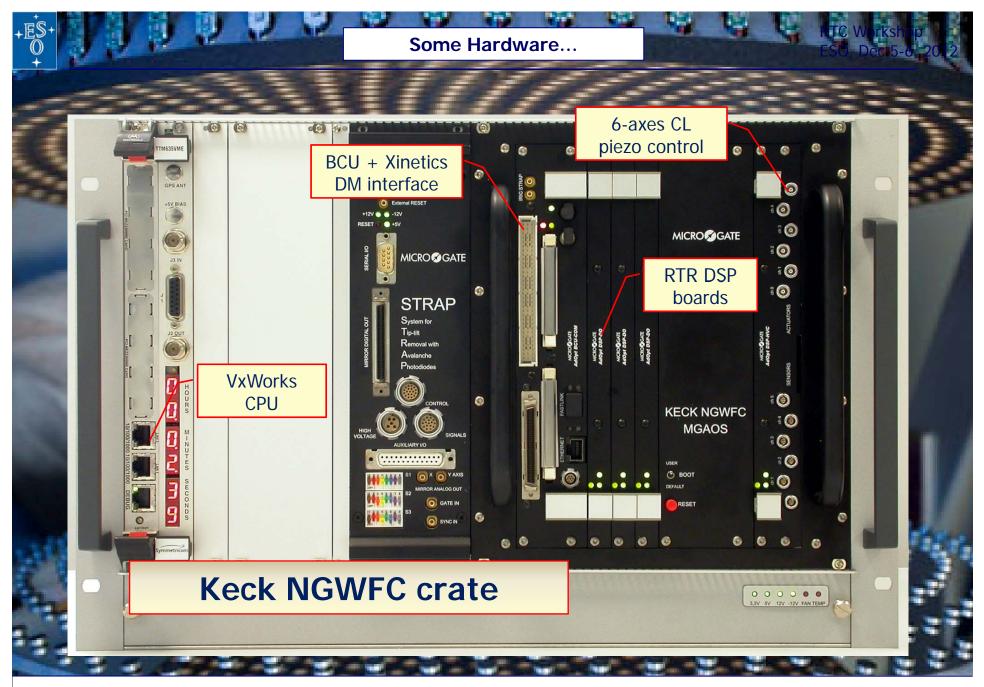

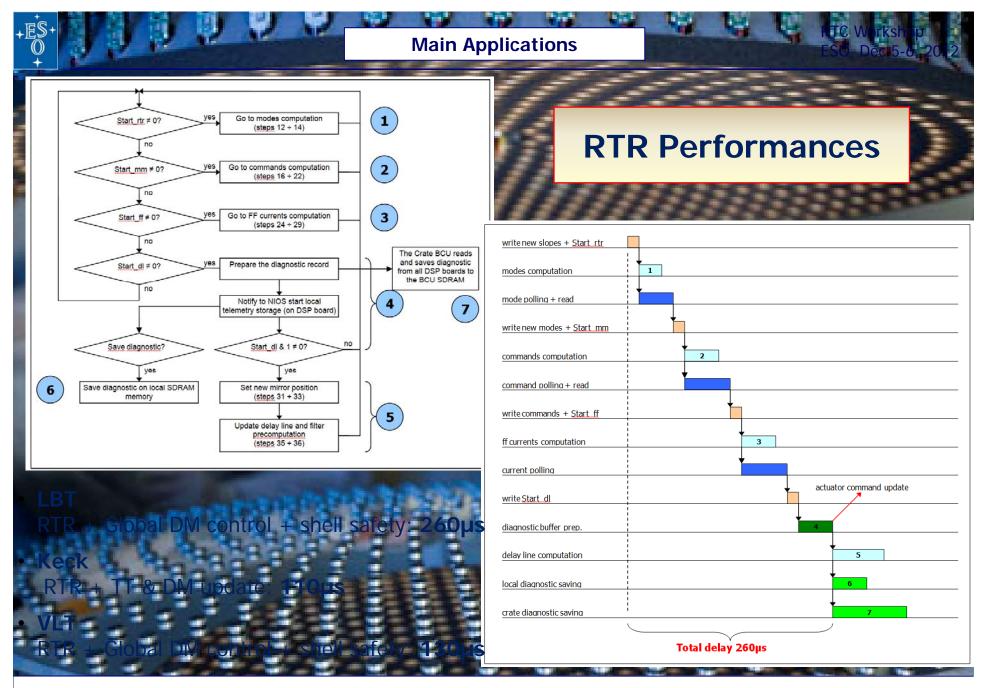

- LBT + Magellan. RTR implemented in the same boards performing the mirror control Kerk disdicated boards for RTR only

- MMT Laser Guide Star Real Time Reconstructor

$$\{\Delta m\}_{i} = [B]_{0}\{S\}_{i} + \dots [B]_{n}\{S\}_{i-n} - [A]_{1}\{\Delta m\}_{i-1} - \dots [A]_{m}\{\Delta m\}_{i-n} \\ \{\Delta p\}_{i} = [m2p]\{\Delta m\}_{i}$$

LET: 3 zeros, 3 poles full state (672 d.o.f) MIMO filter

- Hard real time DSP software runs without operating system (ISR + main lo

- Synchronization through real-ime communication

- · One BCU acts as arbiter and controls 'data recirculation' for parallel processing

- Deterministic timing with extremely low jitter, sub-microsecond level

- Very efficient real-time diagnostic buffering system, implemented on hardware

Real-time system 'hidden' behind a host machine interfaced by standard Ethernet LBT. Linux workstation (designed and implemented by INAF-Arcetri)

Keck and VLD single board computer running under VxWorks

irect-access to

### FPGA-only based control

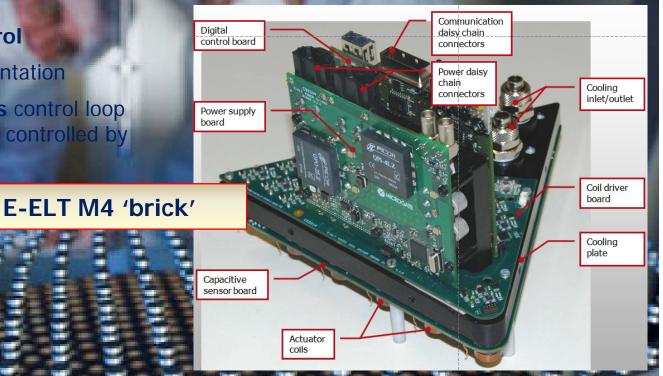

## ELT M4 deformable mirror control unit

- Ine Replace ble Unit compleheading ~30 actuators, control electronics and sup Clobal control moved away from adaptive unit → on-board power minimized

- · Simplified interfaces and harness (supply, data, cooling)

- Sound maintenance concept, maximize system availability

- FPGA-based local control

- Parallel/pipelined implementation

- Minimum latency, ~400ns control loop computational delay, 36ch controlled by one single FPGA

experience with dedicated electronics

On

Importance of an abs

(is it really custom? More than 500 MIC DSP hoards produced ...)

- COTS are not trouble-free and support over system lifetime can be an issue

- Expandability, true parallel architecture, very efficient data recirculation are mandatory for demanding processing application (real world is never just a matrix-vector multiply...)

- Hardware acceleration is appealing but development/debugging time shall not be underestimated (FPGA vs. DSP, HW vs. SW)

ayer to hide the hard

Diagnostic/telemetry tasks shall be carefully evaluated unced for independent paths for real-time and diagnostic communication

are complexity and to de

The Contactless Deformable Mirror control electronics development remains an impor niche for Microgate (it's not only real time processing...)

- For ELT-class DMs, with several thousands of actuators, it is more effective to dedecate global DM control computation (motivations: on board dissipation, well defined modular design, maintainability, ...)  $\rightarrow$  comparable problem and complexity of AO RTR

- We also intend to remain in the AO RTC field

- Therefore, we are about starting a development project (partially founded by ProvBZ), with the goal of implementing an acceleration hardware, hosted on standard PCs, with a flexible and modular software approach, and well aligned with the ELTs standard interfaces. Detailed workplan still under definition

f Morandi

rot Ramab